2 coprocessor 15 definition, 1 register 0 – id, Coprocessor 15 definition -2 5.2.1 – Intel STRONGARM SA-1100 User Manual

Page 46: Register 0 – id -2

5-2

SA-1100

Developer’s Manual

Coprocessors

5.2

Coprocessor 15 Definition

The SA-1100 coprocessor 15 contains registers that control the cache, MMU, and write buffer

operation as well as some clocking functions. These registers are accessed using CPRT instructions

to coprocessor 15 with the processor in any privileged mode. Only some of registers 0–15 are

valid; the result of an access to an invalid register is unpredictable.

lists the coprocessor

15 control registers.

5.2.1

Register 0 – ID

Register 0 is a read-only register that returns an architecture and implementation-defined

identification for the device.identification for the device.

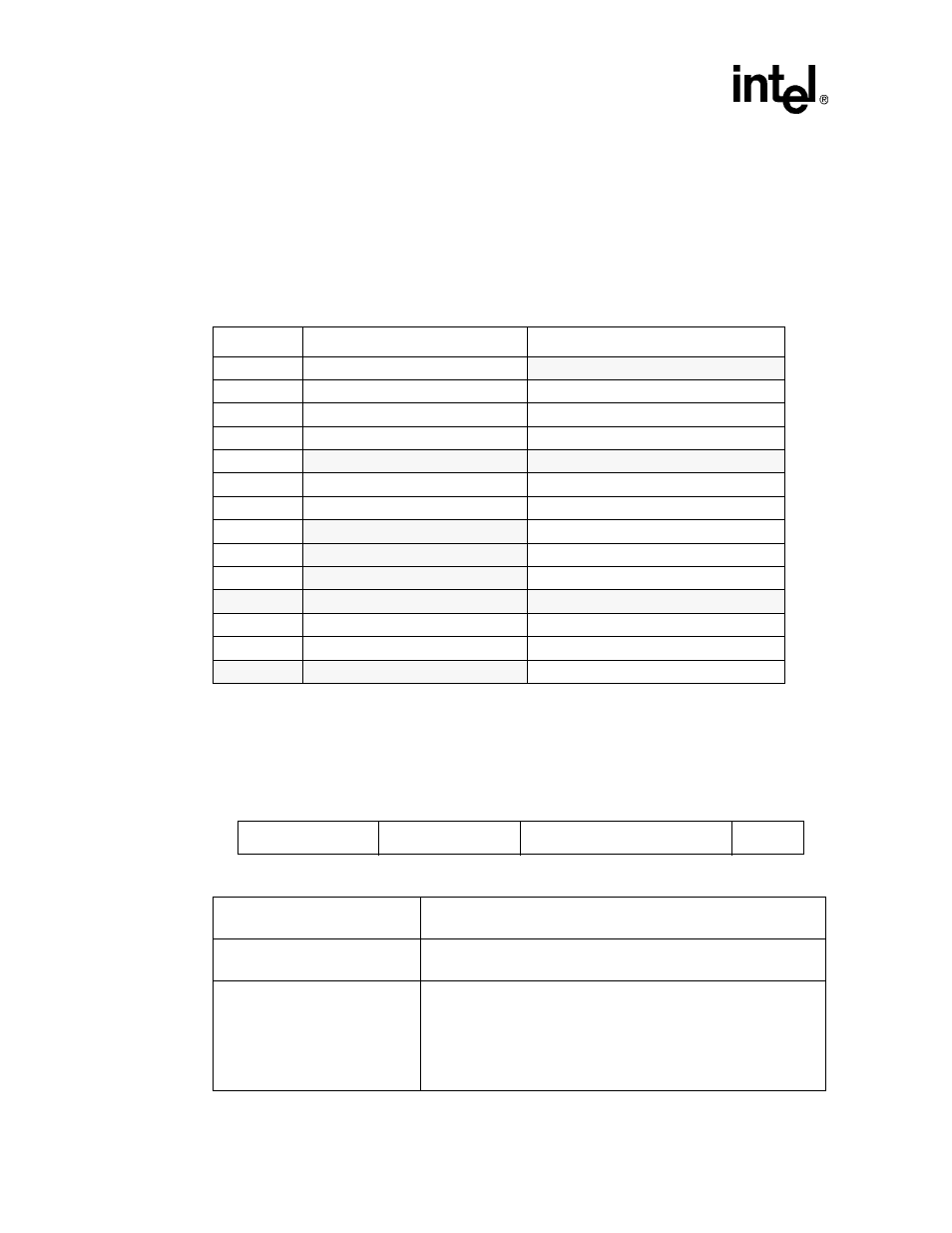

Table 5-1.

Cache and MMU Control Registers (Coprocessor 15)

Register

Register Reads

Register Writes

0

ID

RESERVED

1

Control

Control

2

Translation table base

Translation table base

3

Domain access control

Domain access control

4

RESERVED

RESERVED

5

Fault status

Fault status

6

Fault address

Fault address

7

RESERVED

Cache operations

8

RESERVED

TLB operations

9

RESERVED

Read buffer operations

10..12

RESERVED

RESERVED

13

Read process ID (PID)

Write process ID (PID)

14

Read breakpoint

Write breakpoint

15

RESERVED

Test, clock, and idle

0

3

4

15

16

23

24

31

44

Stepping

Part Number

Architecture Version

Architecture Version

ARM architecture version

01 = Version 4

Part Number

Part number

A11 = SA1100

Stepping

Stepping revision of SA-1100

1 = B stepping

2 = C stepping

8 = D stepping

9 = E stepping

11 = G stepping