Intel STRONGARM SA-1100 User Manual

Page 268

11-118

SA-1100

Developer’s Manual

Peripheral Control Module

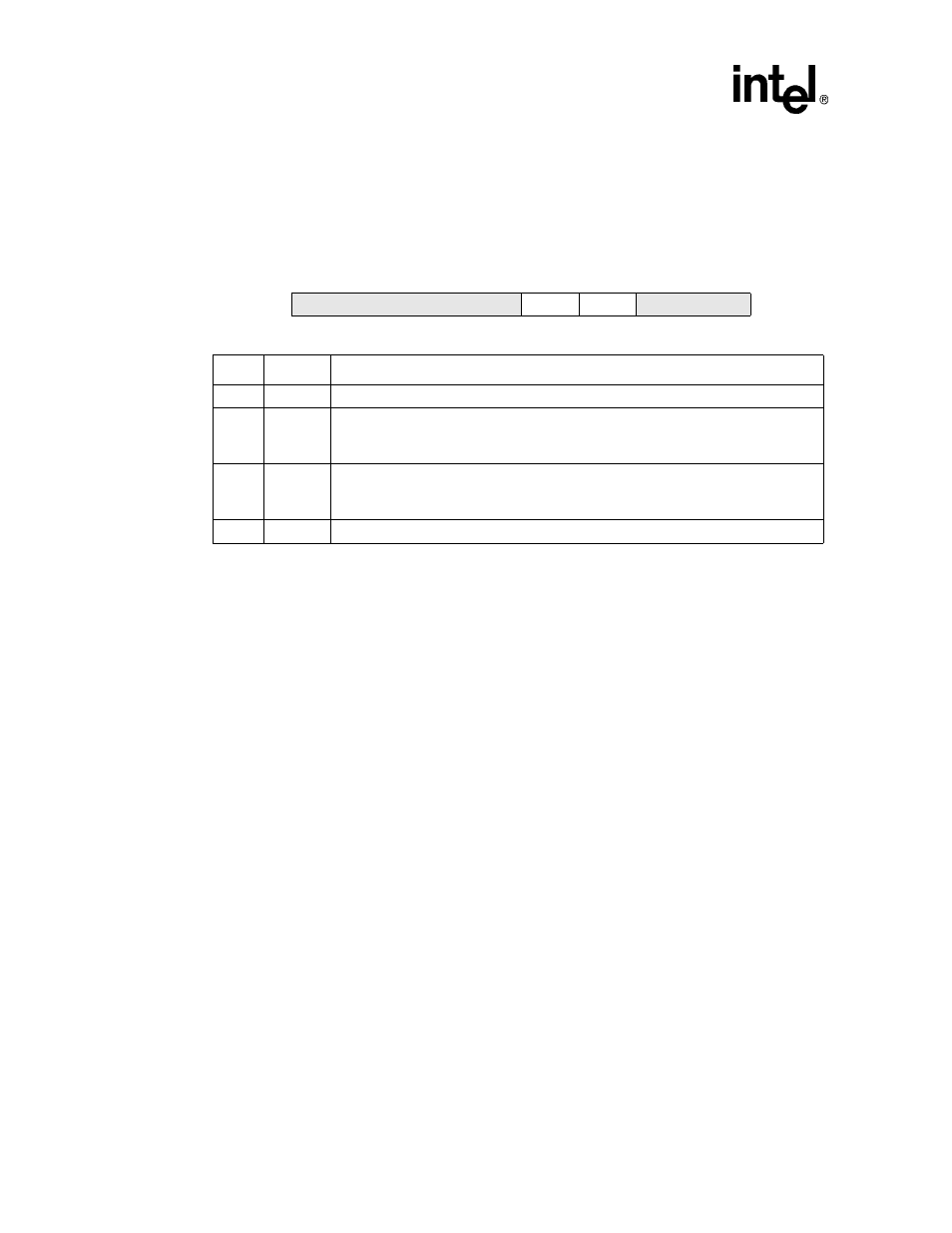

The following table shows the location of the bits within HSSP control register 2. Both bits are set

to one to ensure serial port 2’s pins default to normal “true” data operation following a reset of the

SA-1100. Note that the HSSP and UART must be disabled (RXE=TXE=0) when changing the state

of these bits. Also note that reads of reserved bits return zero and writes have no effect.

Address: 0h 9006 0028

HSCR2

Read/Write

Bit

23

22

21

20

19

18

17

16

Reserved

RXP

TXP

Reserved

Reset

0

0

0

0

1

1

0

0

Bit

Name

Description

17..16

—

Reserved.

18

TXP

Transmit pin polarity select.

0 – Data output from the HSSP, UART, or PPC is first inverted before being output to TXD2.

1 – Data output from the HSSP, UART, or PPC to TXD2 is true or non-inverted data.

19

RXP

Receive pin polarity select.

0 – Data input from RXD2 is first inverted before being used by the HSSP, UART, or PPC.

1 – Data input from RXD2 to the HSSP, UART, or PPC is true or non-inverted data.

23..20

—

Reserved.

- 41210 (64 pages)

- 8xC251TQ (20 pages)

- ENTERPRISE PRINTING SYSTEM (EPS) 4127 (84 pages)

- U3-1L (20 pages)

- 80960HA (104 pages)

- X58 (54 pages)

- ESM-2850 2047285001R (91 pages)

- ATOM US15W (54 pages)

- D915GVWB (4 pages)

- XP-P5CM-GL (28 pages)

- AX965Q (81 pages)

- CORETM 2 DUO MOBILE 320028-001 (42 pages)

- CV700A (63 pages)

- 80C188EA (50 pages)

- X25-M (28 pages)

- XP-P5IM800GV (26 pages)

- IB868 (60 pages)

- D865GVHZ (88 pages)

- IB865 (64 pages)

- Altera P0424-ND (1 page)

- 8086-2 (30 pages)

- IXDP465 (22 pages)

- IWILL P4D (104 pages)

- GA-8I955X PRO (88 pages)

- FSB400 (PC2100) (96 pages)

- D845GLAD (4 pages)

- NAR-3041 (1 page)

- 87C196CA (136 pages)

- G52-M6734XD (74 pages)

- A96134-002 (10 pages)

- Express Routers 9000 (8 pages)

- 82540EP (45 pages)

- D865GLC (94 pages)

- IB850 (69 pages)

- MB898RF (62 pages)

- Arima LH500 (78 pages)

- V09 (33 pages)

- I/O Processor (22 pages)

- M600 (110 pages)

- SE7520JR2 (63 pages)

- SERVER BOARD S5520HCT (30 pages)

- Extensible Firmware Interface (1084 pages)

- GA-8IPXDR-E (70 pages)

- D845EBG2 (4 pages)

- AW8D (80 pages)