5receive fifo service request flag (rfs), Read-only, maskable interrupt) -182, 6receiver overrun status (ror) – Intel STRONGARM SA-1100 User Manual

Page 332: Read/write, nonmaskable interrupt) -182, Peripheral control module

11-182

SA-1100

Developer’s Manual

Peripheral Control Module

11.12.12.5 Receive FIFO Service Request Flag (RFS) (read-only, maskable

interrupt)

The receive FIFO service request flag (RFS) is a read-only bit that is set when the receive FIFO is nearly

filled and requires service to prevent an overrun. RFS is set whenever the receive FIFO has four or more

entries of valid data (half-full or more), and is cleared when it has three or fewer (less than half-full)

entries of data. When the RFS bit is set, an interrupt request is made unless the receive FIFO interrupt

request enable (RIE) bit is cleared. The state of RFS is also sent to the DMA controller, and can be used

to signal a DMA service request. Note that RIE has no effect on the generation of the DMA service

request. After the DMA or CPU fills the FIFO such that four or more locations are filled within the

receive FIFO, the RFS flag (and the service request and/or interrupt) is automatically cleared.

11.12.12.6 Receiver Overrun Status (ROR) (read/write, nonmaskable interrupt)

The receiver overrun status bit (ROR) is a read/write bit that is set when the receive logic attempts

to place data into the receive FIFO after it has been completely filled. Each time a new piece of

data is received, the set signal to the ROR bit is asserted, and the newly received data is discarded.

This process is repeated for each new piece of data received until at least one empty FIFO entry

exists. When the ROR bit is set, an interrupt request is made.

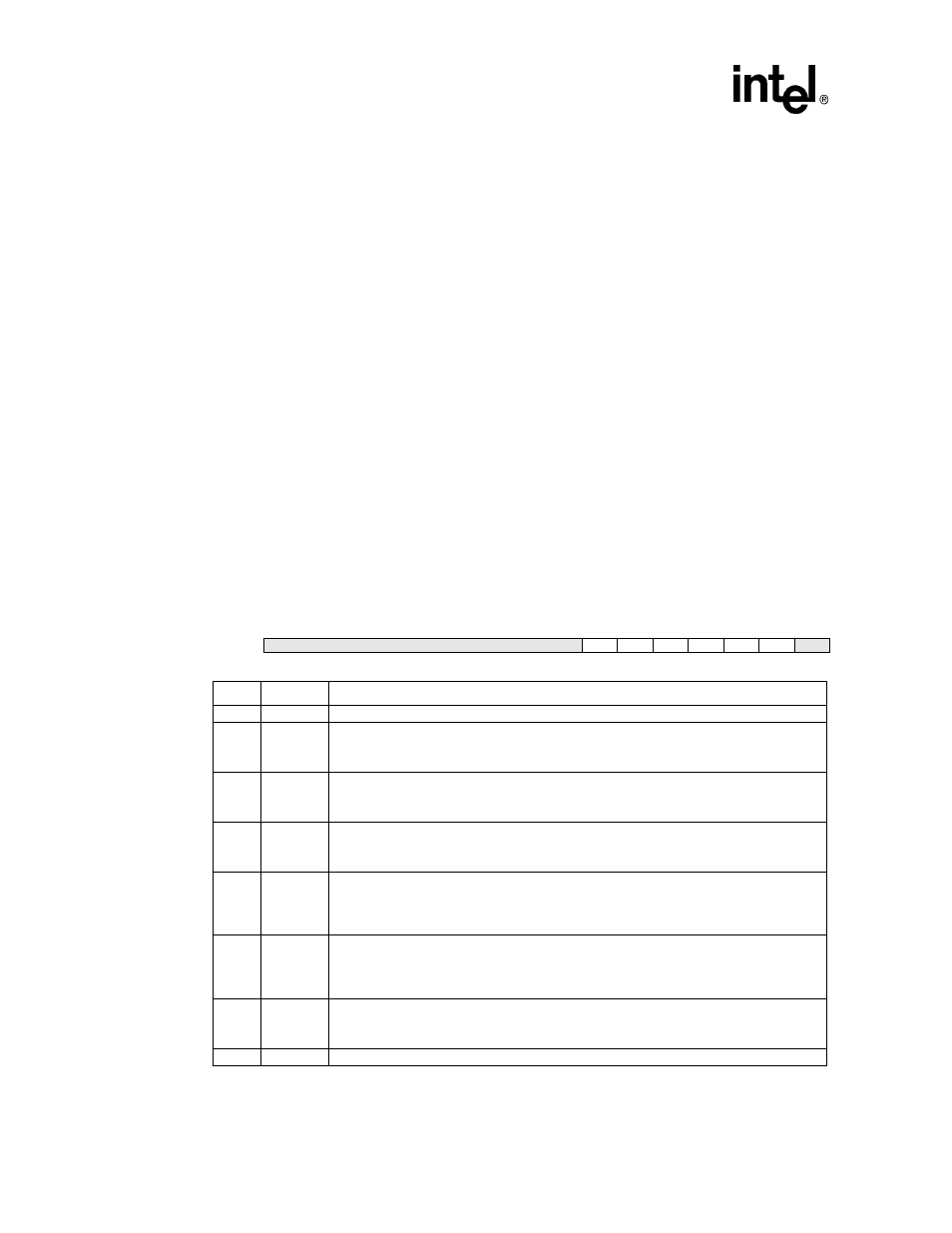

The following table shows the bit locations corresponding to the status and flag bits within the SSP

status register. All bits are read-only except ROR, which is read/write. Writes to TNF, RNE, BSY, TFS,

and RFS have no effect. The reset state of ROR is unknown (indicated by a question mark) and must be

initialized before enabling the SSP. Note that writes to reserved bits are ignored and reads return zeros.

Address: 0h 8007 0074

SSP Status Register: SSSR

Read/Write &

Read-Only

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Reserved

ROR

RFS

TFS

BSY

RNE

TNF

Res

Reset

0

0

0

0

0

0

0

0

0

?

0

0

0

0

1

0

Bit

Name

Description

0

—

Reserved.

1

TNF

Transmit FIFO not full (read-only).

0 – Transmit FIFO is full.

1 – Transmit FIFO is not full.

2

RNE

Receive FIFO not empty (read-only).

0 – Receive FIFO is empty.

1 – Receive FIFO is not empty.

3

BSY

SSP busy flag (read-only).

0 – SSP is idle or disabled.

1 – SSP is currently transmitting and/or receiving a frame (no interrupt generated).

4

TFS

Transmit FIFO service request (read-only).

0 – Transmit FIFO is more than half-full (five or more entries filled) or SSP disabled.

1 – Transmit FIFO is half-full or less (four or fewer entries filled) and SSP operation is

enabled, DMA service request signalled, interrupt request signalled if not masked (if TIE=1).

5

RFS

Receive FIFO service request (read-only).

0 – Receive FIFO is less than half-full (three or fewer entries filled) or SSP disabled.

1 – Receive FIFO is half-full or more (four or more entries filled) and SSP operation is

enabled, DMA service request signalled, interrupt request signalled if not masked (if RIE=1).

6

ROR

Receive FIFO overrun.

0 – Receive FIFO has not experienced an overrun.

1 – Receive logic attempted to place data into receive FIFO while it was full, request interrupt.

15..7

—

Reserved.