7 suspend/resume interrupt mask (srm), 8 reset interrupt mask (rem) – Intel STRONGARM SA-1100 User Manual

Page 215

SA-1100 Developer’s Manual

11-65

Peripheral Control Module

11.8.3.7

Suspend/Resume Interrupt Mask (SRM)

The suspend/resume interrupt mask (SRM) bit is used to mask or enable the suspend/resume

interrupt request. When SRM=1, the interrupt is masked, and the SUSIR/RESIR bits in the

status/interrupt register are not allowed to be set. When SRM=0, the interrupt is enabled, and

whenever a suspend or resume condition occurs, the SUSIR or RESIR bit is set. Note that

programming SRM=1 does not affect the current state of SUSIR/RESIR; it only blocks future zero

to one transitions of SUSIR/RESIR.

11.8.3.8

Reset Interrupt Mask (REM)

The reset interrupt mask (REM) bit is used to mask or enable the reset interrupt request. When

REM=1, the interrupt is masked, and the RSTIR bit in the status/interrupt register is not allowed to

be set. When REM=0, the interrupt is enabled, and whenever the USB host controller issues a reset

to the UDC, the RSTIR bit is set. Note that programming REM=1 does not affect the current state

of RSTIR; it only blocks future zero to one transitions of RSTIR.

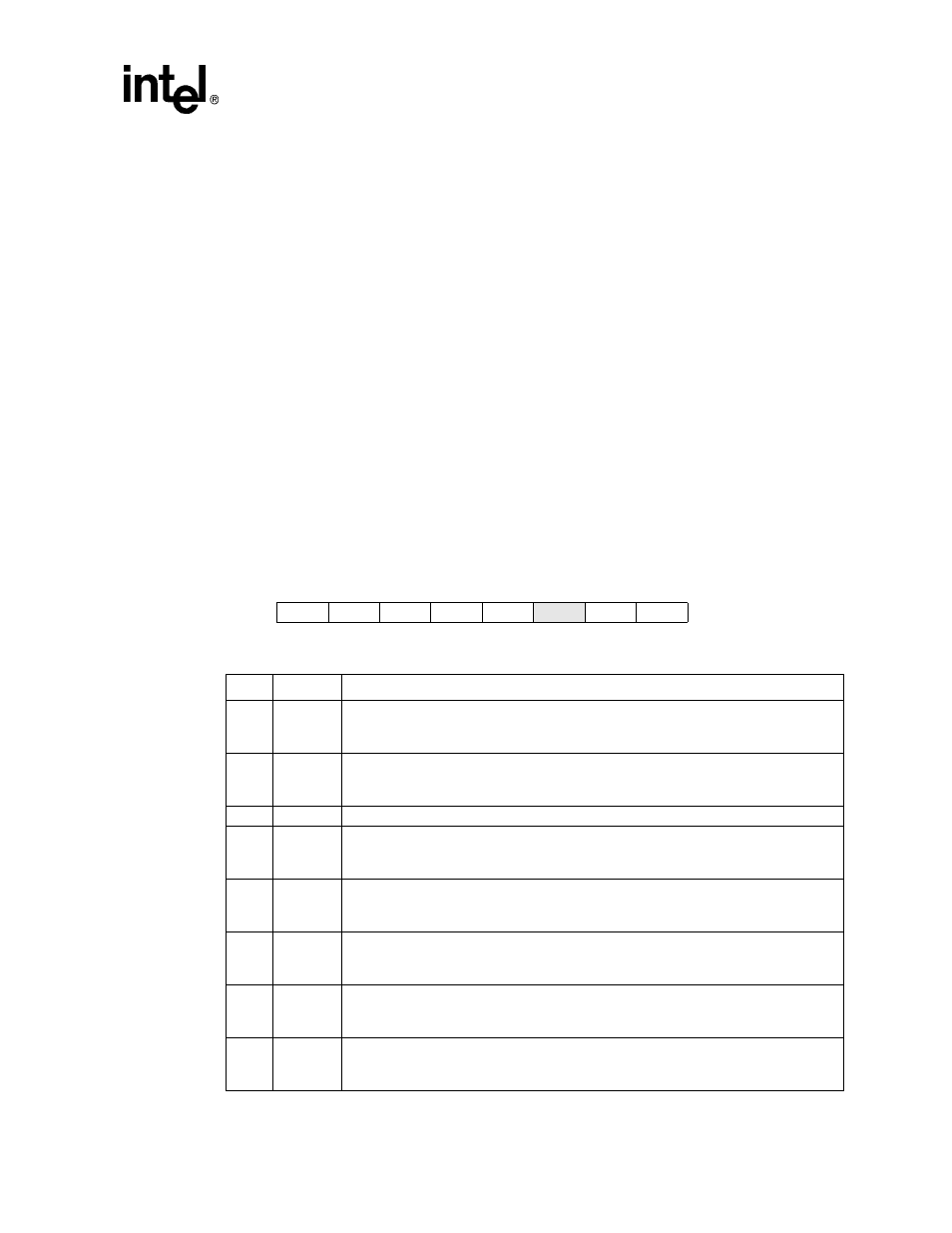

The following table shows the location of the UDE, RIM, and TIM bits in UDC control register

(UDCR). The state of RIM and TIM are unknown and must be initialized before enabling the

UDC. The UDE bit is cleared to zero, disabling the UDC following a reset of the SA-1100. This

gives control of the UDC’s pins to the PPC unit that configures them as inputs. Writes to reserved

bits are ignored and reads return zeros.

Address: 0h 8000 0000

UDCCR

Read/Write & Read Only

Bit

7

6

5

4

3

2

1

0

REM

SRM

TIM

RIM

EIM

Res.

UDA

UDD

Reset

0

1

0

0

0

0

0

1

Bit

Name

Description

0

UDD

UDD disable.

0 – UDD disabled.

1 – UDD enabled, UDC+ and UDC- used for USB serial transmission/reception.

1

UDA

UDC active (read-only).

0 – UDC currently inactive.

1 – UDC currently active.

2

—

Reserved.

3

EIM

Endpoint zero interrupt mask.

0 – Endpoint zero interrupt enabled.

1 – Endpoint zero interrupt disabled.

4

RIM

Receive interrupt mask.

0 – Receive interrupt enabled.

1 – Receive interrupt disabled.

5

TIM

Transmit interrupt mask.

0 – Transmit interrupt enabled.

1 – Transmit interrupt disabled.

6

SRM

Suspend/resume interrupt mask.

0 – Suspend/resume interrupt enabled.

1 – Suspend/resume interrupt disabled.

7

REM

Reset interrupt mask.

0 – Reset interrupt enabled.

1 – Reset interrupt disabled.