2 ppc register definitions, 3 ppc pin direction register – Intel STRONGARM SA-1100 User Manual

Page 335

SA-1100 Developer’s Manual

11-185

Peripheral Control Module

Serial port 1 and serial port 4 both contain two serial-to-parallel engines that operate independently.

However, because each port contains only one set of serial pins, the user can assign these pins to

only one of the two protocols at a time. To allow the user to utilize both protocols, the PPC can

assign one of its two serial-to-parallel engines to the pins that are dedicated to the port, and the

other to a set of GPIO pins. Serial port 1 contains an SDLC and a UART. By setting a bit in the

PPC and the appropriate GAFR and GPDR bits in the GPIO unit, SDLC operation defaults to the

TXD1 and RXD1 pins, and the UART transmits via the GPIO<14> pin and receives via the

GPIO<15> pin. Likewise, serial port 4 contains the MCP and the SSP synchronous serial engines.

The user can configure the PPC and GPIO units to cause the MCP to default to the TXD4, RXD4,

SCLK, and SFRM pins, and the SSP is assigned to GPIO<10> for transmit, GPIO<11> for receive,

GPIO<12> for serial clock, and GPIO<13> for serial frame.

When the SA-1100 is reset or enters sleep mode, the GPIO unit’s registers are reset, which gives

control of the GPIO pins back to the system control module.

11.13.2

PPC Register Definitions

There are five registers within the PPC: one pin direction register, one pin state register, one pin

assignment register, one sleep mode pin direction register, and one pin flag register.

11.13.3

PPC Pin Direction Register

Pin direction is controlled by programming the PPC pin direction register (PPDR). The PPDR

contains individual direction control bits for 22 of the 24 peripheral pins. Serial port 0 has

dedicated pins (UDC+ and UDC-) that are not controlled by the PPC when the UDC is disabled.

Each bit is used only if the corresponding peripheral that it controls is disabled. Provided the

corresponding peripheral is disabled, if the direction bit is programmed to a one, the pin is an

output. If it is programmed to a zero, it is an input. Following reset, all peripherals are disabled,

which causes the PPC to take control of all of their pins. Serial ports 1..3 contain individual enables

for their transmit and receive serial engines. Thus, if only half-duplex transmission is needed, one

pin can be used for serial communication and the other for digital I/O communication. Note that

PPDR is reset such that all the pins are configured as inputs. For reserved bits, writes are ignored

and reads return zero. The following table shows the location of each pin direction bit and to which

peripheral pin it corresponds.

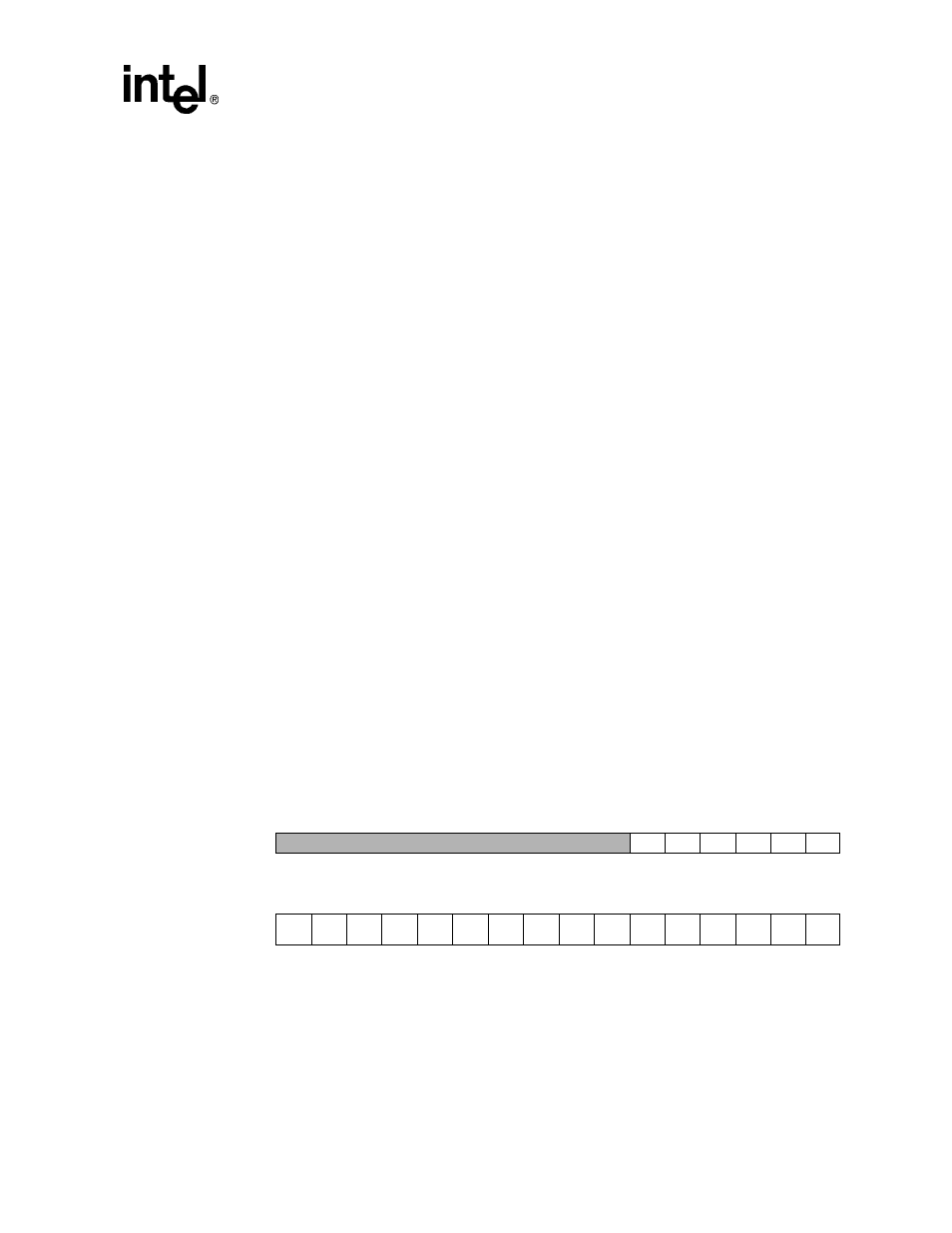

Address: 0h 9006 0000

PPDR: PPC Pin Direction Register

Read/Write

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Reserved

SFRM

SCLK

RXD4

TXD4

RXD3

TXD3

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RXD2

TXD2

RXD1

TXD1

L_

BIAS

L_

FCLK

L_

LCLK

L_

PCLK

LDD

<7>

LDD

<6>

LDD

<5>

LDD

<4>

LDD

<3>

LDD

<2>

LDD

<1>

LDD

<0>

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0