Intel STRONGARM SA-1100 User Manual

Page 170

11-20

SA-1100

Developer’s Manual

Peripheral Control Module

The first palette entry (palette entry 0) also contains an extra field that is used to synchronously

configure the LCD controller at the beginning of each frame. Bits 12 and 13 of the first palette

entry contain a field that is used to select the number of bits per pixel that is to be used in the next

frame (see

). The pixel bit size (PBS) bit-field is decoded by the LCD to correctly

unpack pixel data into nibbles, bytes, 12-bit values, or half-words, and by the palette to tell it how

many address bits are contained in the pixel data it is supplied, configuring the palette size to 16 or

256 entries. Note that 12/16-bit pixel mode bypasses the LCD palette and supplies 12-bit values

directly to the dither logic when passive mode is enabled, or 16-bit values directly to the output

FIFOs when active mode is enabled. The following table shows the encoding of the PBS bit field.

Following the palette buffer is the pixel data buffer that contains one encoded pixel value for each

of the pixels present on the display. The number of pixel data values depends on the size of the

screen (1024 x 768 = 786,432 encoded pixel values).

through

show the

memory organization within the frame buffer for each size pixel encoding. Note that for 4-bit

encodings, 2 pixels are placed into each byte, and for 12-bit encodings the value is right- justified

within a half-word. These figures show the encoded pixel organization for little endian memory

organization. The user can select how the LCD views the ordering of frame buffer pixel entries by

programming the big/little endian select (BLE) bit in LCD control register 0. In big endian mode,

pixel entries are ordered starting with the most significant nibble, byte, or half-word and ending

with the least significant.

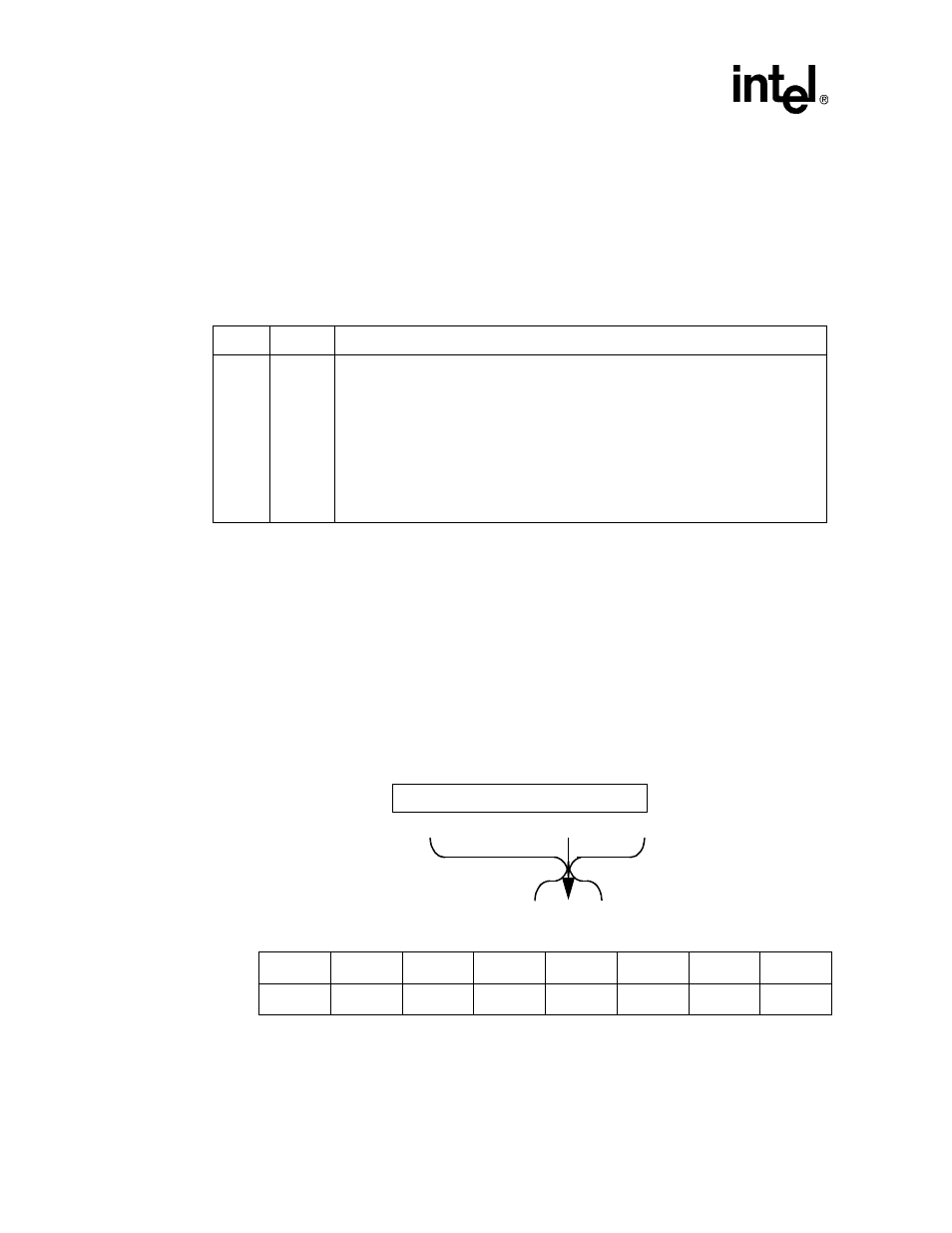

Figure 11-4. 4 Bits Per Pixel Data Memory Organization (Little Endian)

Bit

Name

Description

13..12

PBS

Pixel bit size.

0x – 4 bits per pixel, 16-entry palette, 32 bytes of palette buffer transferred each frame

to palette.

01 – 8 bits per pixel, 256-entry palette, 512 bytes of palette buffer transferred each

frame to palette.

10 – 12 bits per pixel in passive mode (PAS=0), 16 bits per pixel in active mode

(PAS=1). Palette unused, however, 32 bytes of “dummy” palette data is transferred

each frame to palette. Palette data must be zero-filled.

11 – Reserved.

Note: Two 4-bit pixels are packed into each byte, and 12-bit pixels are right justified on

half-word boundaries.

Bit

3

2

1

0

4 bits/pixel

Encoded Pixel Data<3:0>

Bit

31

28

27

24

23

20

19

16

15

12

11

8

7

4

3

0

Base +

0x20

Pixel 7

Pixel 6

Pixel 5

Pixel 4

Pixel 3

Pixel 2

Pixel 1

Pixel 0

Base +

0x24

Pixel 15

Pixel 14

Pixel 13

Pixel 12

Pixel 11

Pixel 10

Pixel 9

Pixel 8

..