6 ppc sleep mode pin direction register, 6 ppc sleep mode pin direction register -190, Peripheral control module – Intel STRONGARM SA-1100 User Manual

Page 340

11-190

SA-1100

Developer’s Manual

Peripheral Control Module

11.13.6

PPC Sleep Mode Pin Direction Register

When sleep mode is entered, reset is asserted to all of the SA-1100’s peripherals and to the PPC unit.

The PPC pin direction register is cleared during a hard, soft, or sleep reset, causing the peripheral pins

under the PPC’s control to be configured as inputs. If this register were also used to determine pin

direction during sleep, the pins would all be configured as inputs. This action would cause any off-chip

device that expects data to be output from the SA-1100 to burn power during sleep because its input

would float. The sleep mode pin direction register (PSDR) prevents this undesired power consumption

by allowing the user to establish peripheral pin direction during and immediately following sleep mode.

When sleep mode is entered, both the peripherals and the PPC are reset; however, PSDR is not reset

like PPDR. Once the user programs PSDR, it retains its data after sleep mode is entered and reset is

asserted. The power manager uses the values in PSDR to determine the direction and state of the 22

peripheral pins. When a sleep mode direction bit is programmed to a zero, the corresponding pin is

configured as an output and is driven low (zero). If it is programmed to a one, it is an input. The

power manager latches the contents of PSDR before VDD is removed from the SA-1100 to maintain

the peripheral pin direction and state after the main power supply is removed. Once VDD is removed,

the data in PSDR is lost and must be reprogrammed after exiting sleep mode. The power manager

contains a control bit called the peripheral control hold (PSSR:PH). This bit is set upon exit from

sleep mode and indicates that the peripheral pins are being held in their sleep state. Following sleep,

the user should first reprogram the peripherals and the PPC, then clear PH (by writing a one to it) in

order to give control of the pins back to the peripheral units. Note that sleep mode invocation causes

RPP to be cleared so that the pins are once again held in their sleep state until the user can set RPP.

See

Chapter 9, “System Control Module”

Because the peripherals are reset when sleep mode is entered, serial port 2’s transmit and receive

pin (TXD2 and RXD2) polarity bits (TXP and RXP) are both reset to one, which configures

transmit and receive data as true or noninverted data. Thus the user need not reprogram these bits

prior to the invocation of sleep mode.

Note that PPSR is initialized only by a hardware or power-on reset (negation of the nRESET pin). It is

not affected by a software reset or a reset that occurs as a result of the SA-1100 entering sleep mode.

Also note that for reserved bits, writes are ignored and reads return zero. The following table shows

the location of each sleep mode pin direction bit and to which peripheral pin it corresponds.

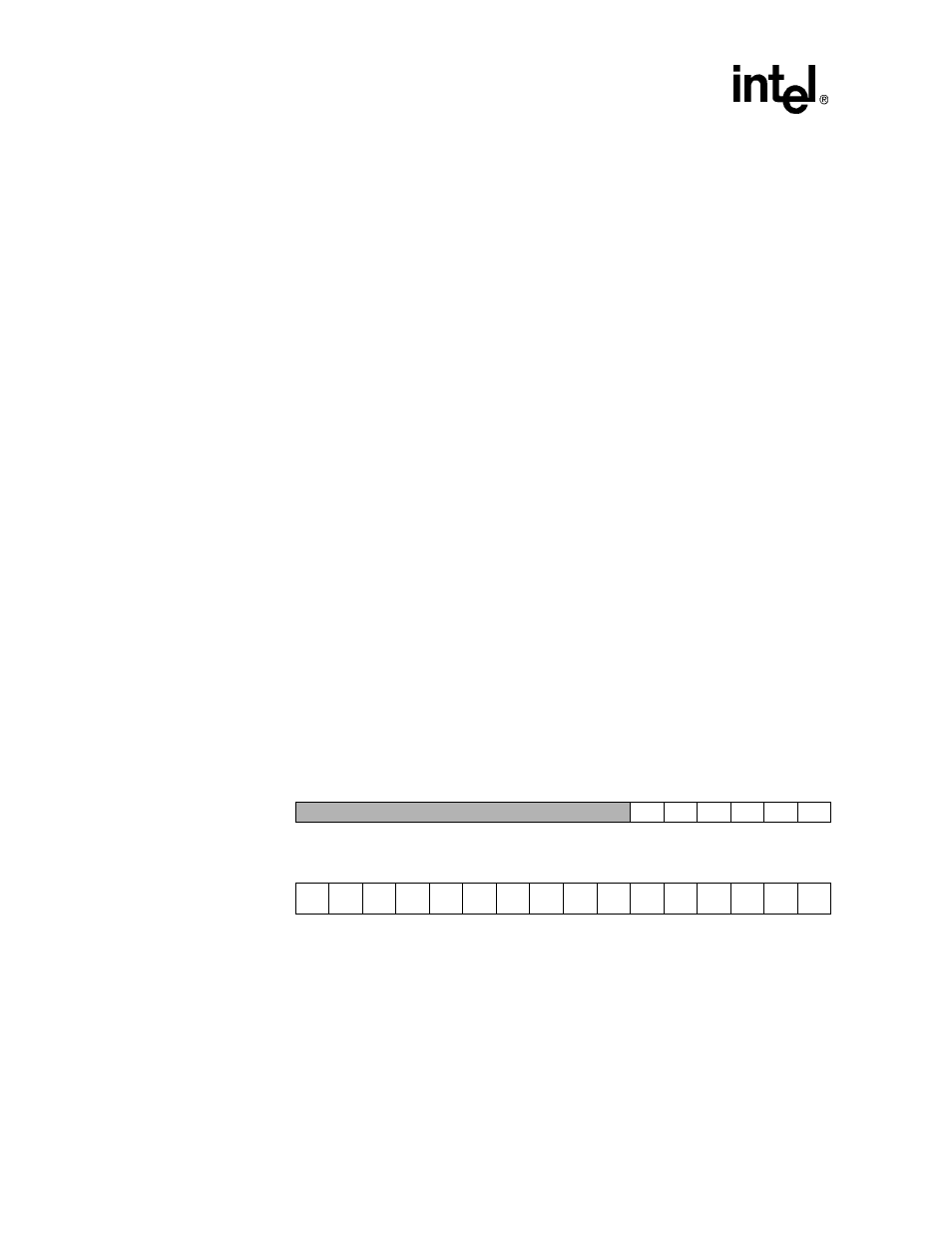

Address: 0h 9006 000C

PSDR: PPC Sleep Mode Pin Direction Register

Read/Write

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Reserved

SFRM

SCLK

RXD4

TXD4

RXD3

TXD3

Hard Reset

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RXD

2

TXD2

RXD1

TXD1

L_

BIAS

L_

FCLK

L_

LCLK

L_

PCLK

LDD

<7>

LDD

<6>

LDD

<5>

LDD

<4>

LDD

<3>

LDD

<2>

LDD

<1>

LDD

<0>

Hard Reset

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1