1 interrupt controller pending register (icpr), 1 interrupt controller pending register (icpr) -12, System control module – Intel STRONGARM SA-1100 User Manual

Page 82

9-12

SA-1100

Developer’s Manual

System Control Module

9.2.1.1

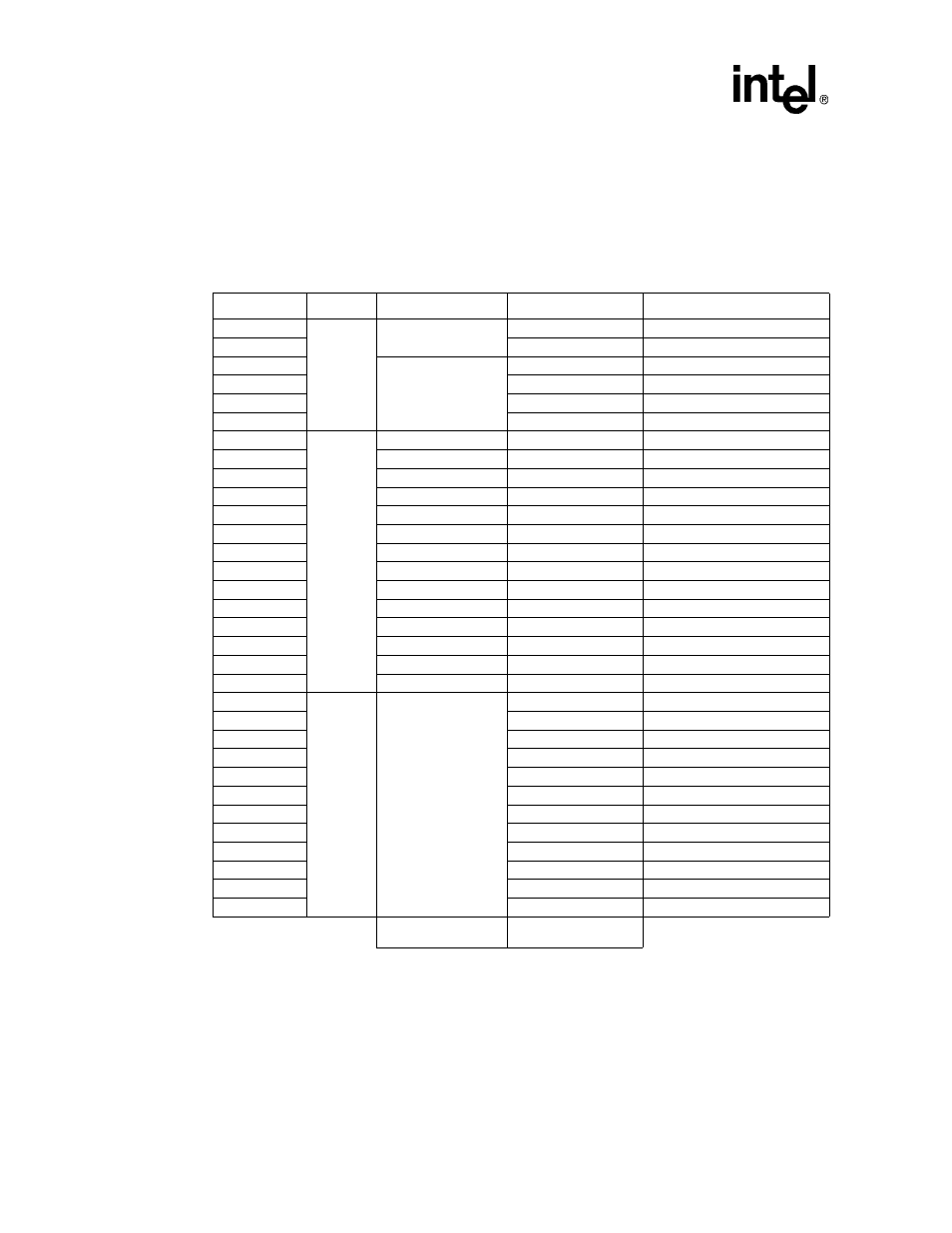

Interrupt Controller Pending Register (ICPR)

The ICPR is a 32-bit read-only register that shows all active interrupts in the system. These bits are

not affected by the state of the mask register (ICMR). The following table shows the pending

interrupt source assigned to each bit position in the ICPR. Also included in the table are the source

units for the interrupts and the number of second-level interrupts associated with each. For more

detail on the second-level interrupts, see the section describing that unit.

Several units have more than one source per interrupt signal. When an interrupt is signalled from

one of these units, the interrupt handler routine identifies which interrupt was signalled using the

interrupt controller’s flag register (this identifies the unit that made the request, but not the exact

source). The handler then reads the interrupting unit’s status register to identify which source

within the unit signalled the interrupt. For all interrupts that have one corresponding source, the

interrupt handler routine needs to use only the interrupt controller’s registers to identify the exact

cause of the interrupt.

Bit Position

Unit

Source Module

# of Level 2 Sources

Bit Field Description

IP<31>

System

Real-time clock

1

RTC equals alarm register.

IP<30>

1

One Hz clock TIC occurred.

IP<29>

Operating system timer

1

OS timer equals match register 3.

IP<28>

1

OS timer equals match register 2.

IP<27>

1

OS timer equals match register 1.

IP<26>

1

OS timer equals match register 0.

IP<25>

Peripheral

DMA controller

3

Channel 5 service request.

IP<24>

3

Channel 4 service request.

IP<23>

3

Channel 3 service request.

IP<22>

3

Channel 2 service request.

IP<21>

3

Channel 1 service request.

IP<20>

3

Channel 0 service request.

IP<19>

Serial port 4b

3

SSP service request.

IP<18>

Serial port 4a

8

MCP service request.

IP<17>

Serial port 3

6

UART service request.

IP<16>

Serial port 2

6+6

UART/HSSP service request.

IP<15>

Serial port 1b

6

UART service request.

IP<14>

Serial port 1a

5

SDLC service request.

IP<13>

Serial port 0

6

UDC service request.

IP<12>

LCD controller

12

LCD controller service request.

IP<11>

System

General-purpose I/O

17

“OR” of GPIO edge detects 27-11.

IP<10>

1

GPIO<10> edge detect.

IP<9>

1

GPIO<9> edge detect.

IP<8>

1

GPIO<8> edge detect.

IP<7>

1

GPIO<7> edge detect.

IP<6>

1

GPIO<6> edge detect.

IP<5>

1

GPIO<5> edge detect.

IP<4>

1

GPIO<4> edge detect.

IP<3>

1

GPIO<3> edge detect.

IP<2>

1

GPIO<2> edge detect.

IP<1>

1

GPIO<1> edge detect.

IP<0>

1

GPIO<0> edge detect.

Total level 2 interrupt

sources

110