Intel STRONGARM SA-1100 User Manual

Page 341

SA-1100 Developer’s Manual

11-191

Peripheral Control Module

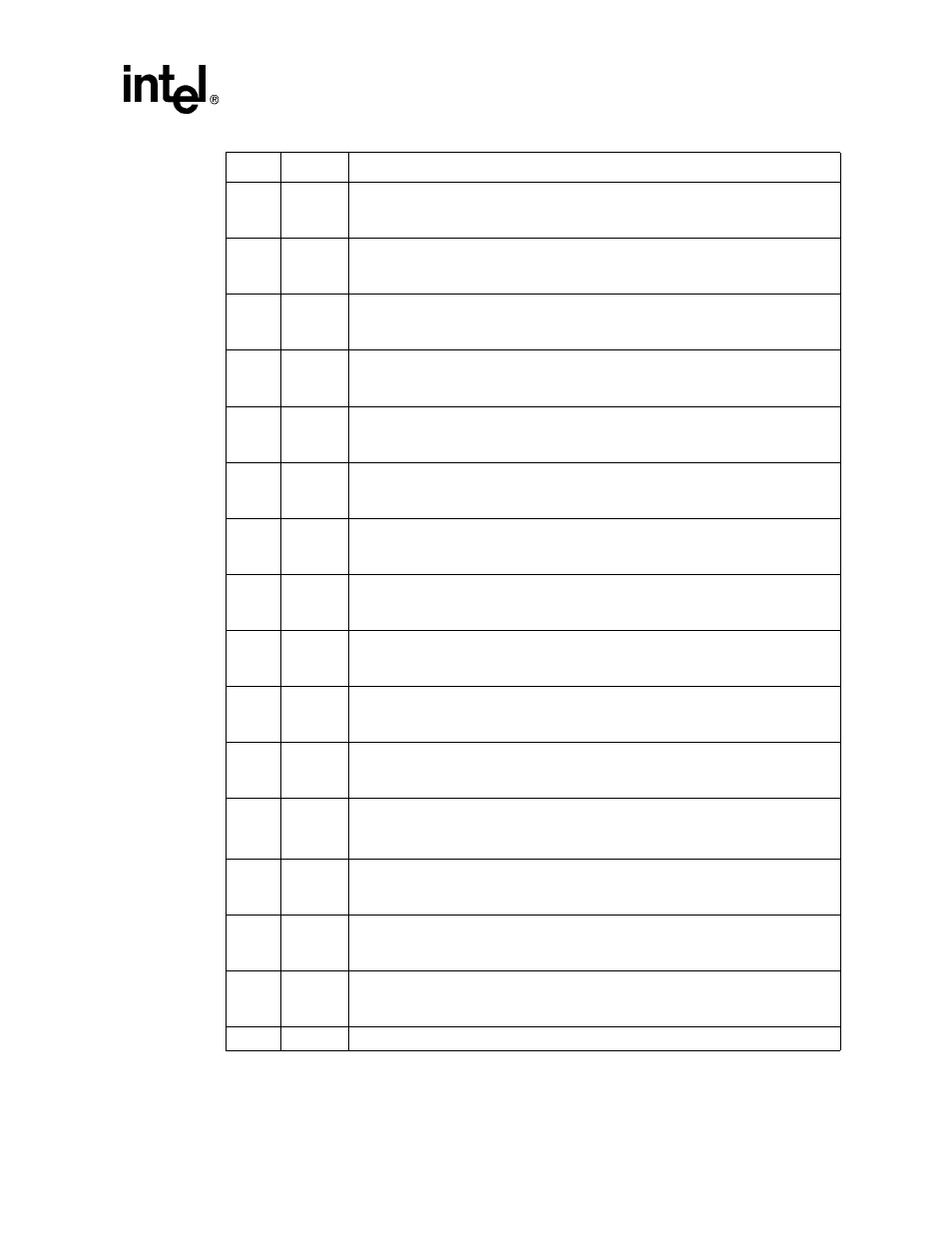

Bit

Name

Description

7..0

LDD<7:0

>

LCD data sleep mode pin direction.

0 – LCD data pin configured as output and is driven low during sleep.

1 – LCD data pin configured as input during sleep.

8

L_PCLK

LCD pixel clock sleep mode pin direction.

0 – LCD pixel clock pin configured as output and is driven low during sleep.

1 – LCD pixel clock pin configured as input during sleep.

9

L_LCLK

LCD line clock sleep mode pin direction.

0 – LCD line clock pin configured as output and is driven low during sleep.

1 – LCD line clock pin configured as input during sleep.

10

L_FCLK

LCD frame clock sleep mode pin direction.

0 – LCD frame clock pin configured as output and is driven low during sleep.

1 – LCD frame clock pin configured as input during sleep.

11

L_BIAS

LCD ac bias sleep mode pin direction.

0 – LCD ac bias pin configured as output and is driven low during sleep.

1 – LCD ac bias pin configured as input during sleep.

12

TXD1

Serial port 1: SDLC/UART transmit sleep mode pin direction.

0 – Transmit pin configured as output and is driven low during sleep.

1 – Transmit pin configured as input during sleep.

13

RXD1

Serial port 1: SDLC/UART receive sleep mode pin direction.

0 – Receive pin configured as output and is driven low during sleep.

1 – Receive pin configured as input during sleep.

14

TXD2

Serial port 2: IPC transmit sleep mode pin direction.

0 – Transmit pin configured as output and is driven low during sleep.

1 – Transmit pin configured as input during sleep.

15

RXD2

Serial port 2: IPC receive sleep mode pin direction.

0 – Receive pin configured as output and is driven low during sleep.

1 – Receive pin configured as input during sleep.

16

TXD3

Serial port 3: UART transmit sleep mode pin direction.

0 – Transmit pin configured as output and is driven low during sleep.

1 – Transmit pin configured as input during sleep.

17

RXD3

Serial port 3: UART receive sleep mode pin direction.

0 – Receive pin configured as output and is driven low during sleep.

1 – Receive pin configured as input during sleep.

18

TXD4

Serial port 4: MCP/SSP transmit sleep mode pin direction.

0 – Transmit pin configured as output and is driven low during sleep.

1 – Transmit pin configured as input during sleep.

19

RXD4

Serial port 4: MCP/SSP receive sleep mode pin direction.

0 – Receive pin configured as output and is driven low during sleep.

1 – Receive pin configured as input during sleep.

20

SCLK

Serial port 4: MCP/SSP serial clock sleep mode pin direction.

0 – Serial clock pin configured as output and is driven low during sleep.

1 – Serial clock pin configured as input during sleep.

21

SFRM

Serial port 4: MCP/SSP serial frame sleep mode pin direction.

0 – Serial frame pin configured as output and is driven low during sleep.

1 – Serial frame pin configured as input during sleep.

31..22

—

Reserved.