Intel STRONGARM SA-1100 User Manual

Page 248

11-98

SA-1100

Developer’s Manual

Peripheral Control Module

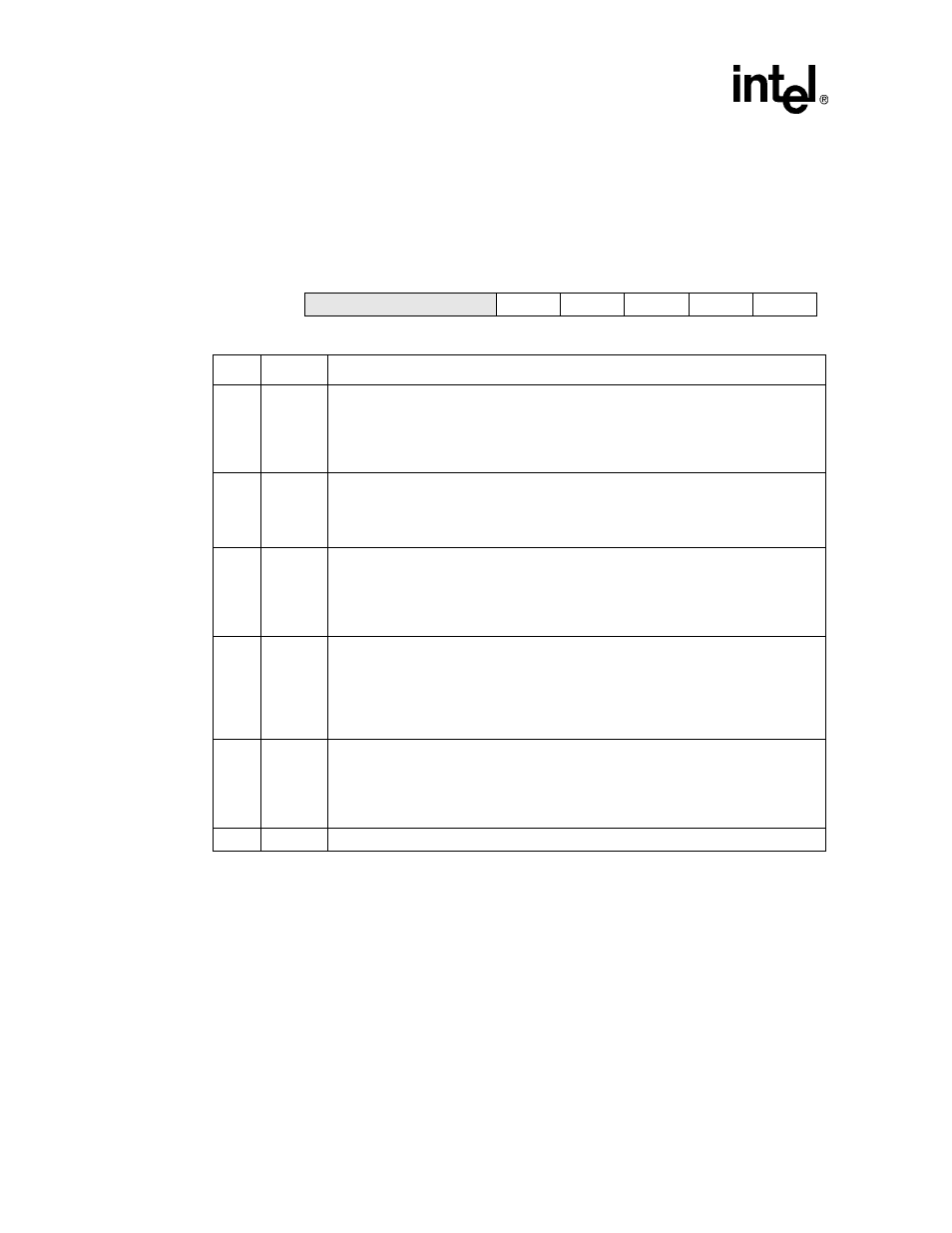

The following table shows the bit locations corresponding to the status and flag bits within SDLC

status register 0. Note that the reset state of all writable status bits is unknown (indicated by

question marks) and must be cleared (by writing a one to them) before enabling the SDLC. Also

note that writes to reserved bits are ignored and reads return zeros.

Address: 0h 8002 0080

SDSR0

Read/Write & Read-Only

Bit

7

6

5

4

3

2

1

0

Reserved

RFS

TFS

RAB

TUR

EIF

Reset

0

0

0

0

0

?

?

?

Bit

Name

Description

0

EIF

Error in FIFO (read-only).

0 – Bits 8..10 are not set within any of the four bottom entries of the receive FIFO;

receive FIFO DMA service requests are enabled.

1 – One or more tag bits (8..10) are set within one or more of the bottom four entries of

the receive FIFO; request interrupt, disable receive FIFO DMA service requests.

1

TUR

Transmit FIFO underrun.

0 –Transmit FIFO has not experienced an underrun.

1 – Transmit logic attempted to fetch data from transmit FIFO while it was empty;

interrupt request signalled if not masked (if TUS=1).

2

RAB

Receiver abort.

0 – No abort has been detected for the incoming frame.

1 – Abort detected during receipt of incoming frame, seven or more ones detected on

receive pin, EOF bit set in receive FIFO next to last piece of “good” data received before

the abort, interrupt requested if it is enabled (if RAE=1).

3

TFS

Transmit FIFO service request (read-only).

0 – Transmit FIFO is more than half-full (five or more entries filled) or transmitter

disabled.

1 – Transmit FIFO is half-full or less (four or fewer entries filled) and transmitter operation

is enabled. DMA service request signalled, interrupt request signalled if it is enabled (if

TIE=1).

4

RFS

Receive FIFO service request (read-only).

0 – Receive FIFO contains seven or fewer entries of data or receiver disabled.

1 – Receive FIFO is one- to two-thirds full (contains 5, 6, 7, or 8 entries of data) or more,

receiver operation is enabled, DMA service request signalled, and interrupt request

signalled if it is enabled (if RIE=1).

7..5

—

Reserved.