9 dma channel 1 current address register, 9 dma channel 1 current address register -44, Peripheral control module – Intel STRONGARM SA-1100 User Manual

Page 194: Len= 0 → 1)

11-44

SA-1100

Developer’s Manual

Peripheral Control Module

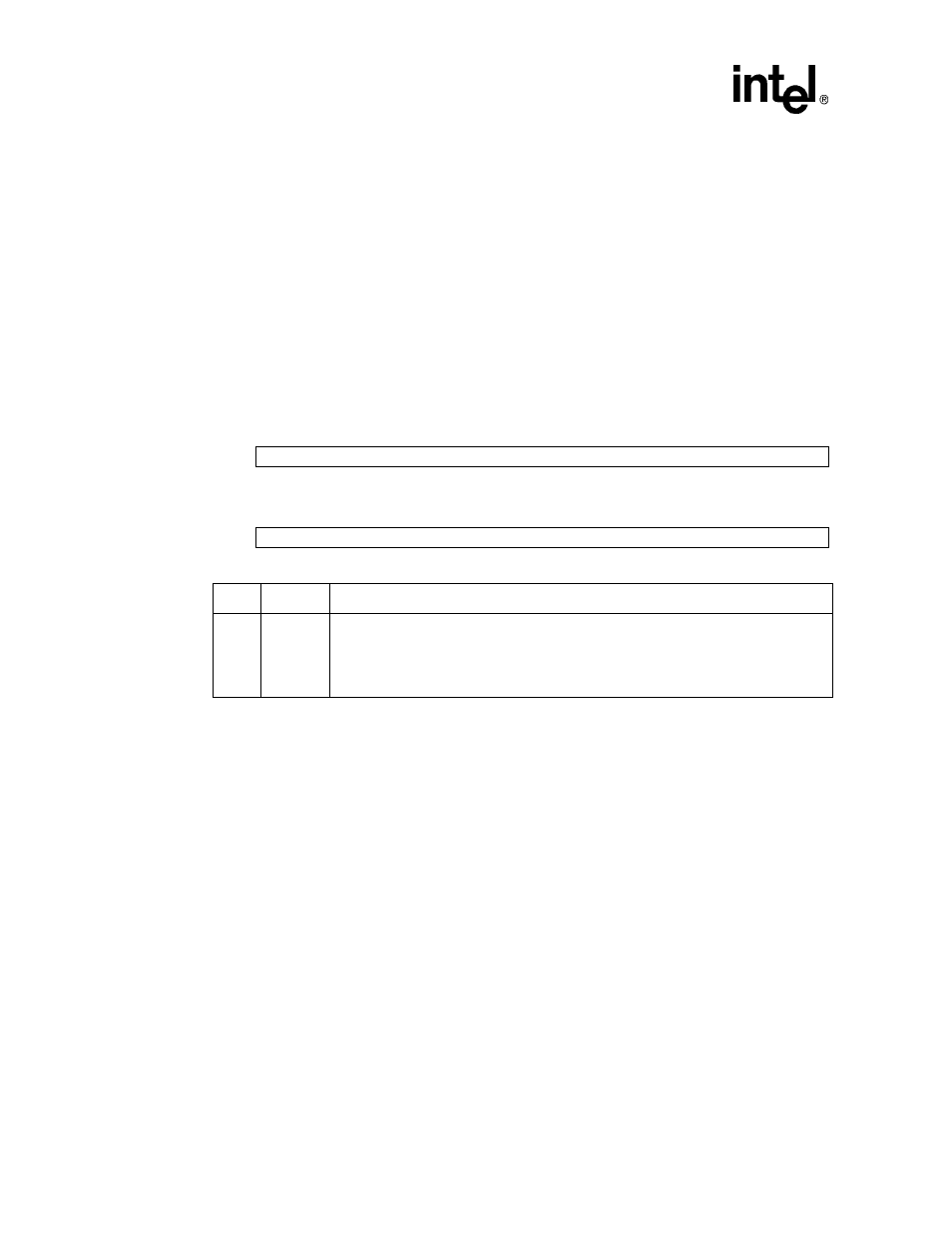

11.7.9

DMA Channel 1 Current Address Register

DMA channel 1 current address register (DCAR1) is a 32-bit read-only register that is used by

DMA channel 1 to keep track of the address of the DMA transfer currently in progress or the

address of the next DMA transfer. Any time the LCD is first enabled

(LEN= 0

→

1)

or the value in

the current address pointer register equals the calculated end address value, the contents of the base

address pointer register is transferred to the current address pointer. This register can be read to

determine the approximate line that the LCD controller is currently processing and driving out to

the display. It is also useful to read this register just before writing the DMA’s base address pointer

to ensure that the end of frame is not about to occur, which means that the base address pointer is

about to be transferred to the current address pointer. Note that DCAR1 is a read-only register that

is not reset and is not initialized until the LCD is first enabled, causing the contents of the base

address register to be transferred to it; question marks indicate that the values are unknown at reset.

.

Address: 0h B010 0014

DCAR1: DMA Channel 1 Current Address Register

Read-Only

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

DMA Channel 1 Current Address Pointer

Reset

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

-

-

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

DMA Channel 1 Current Address Pointer

Reset

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

Bit

Name

Description

31..0

DCAR1

DMA channel 1 current address pointer.

Read-only register. Continuously reflects the current address that DMA channel 1 is

transferring from or will use in the next transfer. Base address register is transferred to

this register whenever the LCD is enabled (LEN= 0

→

1) and when the current address is

equal to the calculated end address of the buffer.