4 udc address register, 5 udc out max packet register – Intel STRONGARM SA-1100 User Manual

Page 216

11-66

SA-1100

Developer’s Manual

Peripheral Control Module

11.8.4

UDC Address Register

The UDC address register contains a 7-bit field that holds the device address. After a reset of the

UDC core, the value of this register is zero. The CPU writes an address to this register when it

receives a SET_ADDRESS from the USB host controller. It extracts the address assigned to the

UDC from the SET_ADDRESS command and writes the value into the UDC address register. The

new address is not propagated to the rest of the UDC core until the SET_ADDRESS command is

completed with an acknowledged handshake from the UDC.

11.8.5

UDC OUT Max Packet Register

The UDC OUT max packet register holds the value of the maximum packet size the UDC core will

accept minus one. This is done in order to accommodate maximum packets of 256 bytes, without

going to a max packet field of more than 8 bits. In order to accept packets up to 256 bytes, a value

of 0xff (255) should be written into the OUT max packet register. At reset the OUT max packet

register contains 0x08, and will therefore accept packets of length 9 bits or less.

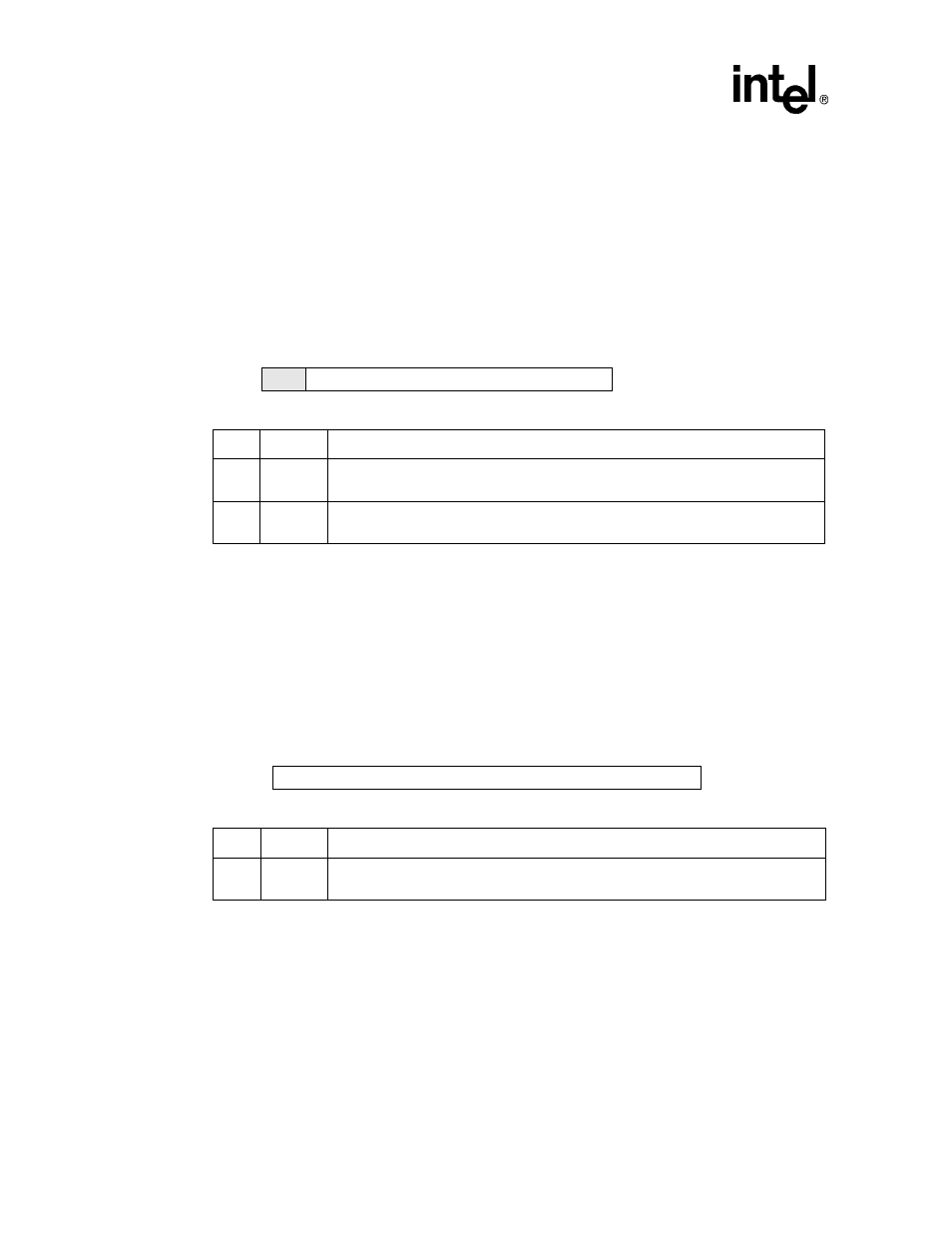

Address: 0h 8000 0004

UDCAR

Read/Write

Bit

7

6

5

4

3

2

1

0

Res

7-bit Function Address

Reset

0

0

0

0

0

0

0

0

Bit

Name

Description

7

—

Reserved.

Always read zero.

6..0

Address

Function address field

7-bit function address. Reset to all zero.

Address: 0h 8000 0008

UDCOMP

Read/Write

Bit

7

6

5

4

3

2

1

0

Max Packet Size - 1

Reset

0

0

0

0

1

0

0

0

Bit

Name

Description

7..0

OUT

MaxP

OUT max packet size.

8-bit field containing the value of the maximum packet size minus one.