Peripheral control module – Intel STRONGARM SA-1100 User Manual

Page 195

SA-1100 Developer’s Manual

11-45

Peripheral Control Module

11.7.10

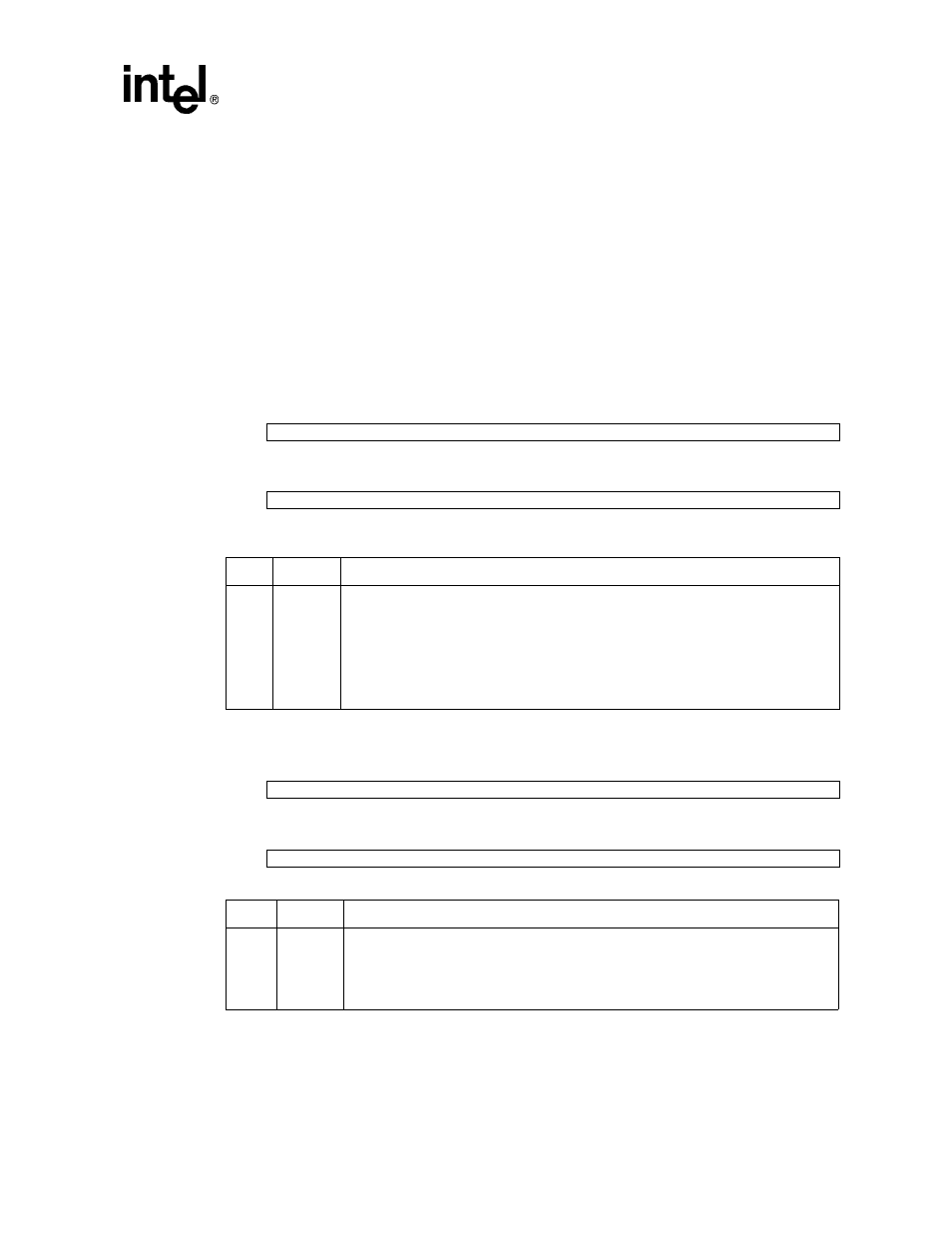

DMA Channel 2 Base and Current Address Registers

DMA channel 2’s base and current address registers (DBAR2 and DCAR2) function exactly like

DMA channel 1’s except that they are used exclusively for dual-panel operation. (See the preceding

sections.) When SDS=1, DMA channel 2 is used to supply frame buffer data to the lower half of the

display. Note that the palette buffer, which resides within the first 16 or 256 entries of the frame buffer,

is utilized only by DMA channel 1. The user should not place palette entries into the frame buffer for

DMA channel 2. The base address for channel 2 points to the first encoded pixel values for the lower

half of the display. For dual-panel operation, the user must perform the following sequence in order:

disable the LCD (LEN=0), program dual-panel mode (SDS= 0

→

1), write the upper panel DMA base

address, write the lower DMA base address and enable the LCD (LEN= 0

→

1). The following figures

show the format of these registers; question marks indicate that the values are unknown at reset.

Address: 0h B010 0018

DBAR2: DMA Channel 2 Base Address Register

Read/Write

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

DMA Channel 2 Base Address Pointer

Reset

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

DMA Channel 2 Base Address Pointer

Reset

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

Bit

Name

Description

31..0

DBAR2

DMA channel 2 base address pointer.

Used to specify the base address of the frame buffer within off-chip memory for the lower

half of the display in dual-panel operation. Value in DBAR2 is transferred to current

address pointer register 2 when LCD is first enabled (LEN= 0

→

1) and when the current

address pointer value reaches the end-of-frame buffer. DBAR2 should be written only

when the LCD is disabled or immediately after an interrupt is generated by setting the

base address update status (BAU) bit. The base address must be on a quadword

boundary. The user must always write bits 0 through 3 to zero.

Address: 0h B010 001C

DCAR2: DMA Channel 2 Current Address Register

Read-Only

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

DMA Channel 2 Current Address Pointer

Reset

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

DMA Channel 2 Current Address Pointer

Reset

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

Bit

Name

Description

31..0

DCAR2

DMA channel 2 current address pointer.

Read-only register. Continuously reflects the current address that DMA channel 2 is

transferring from or will use in the next transfer. Base address register is transferred to

this register whenever the LCD is first enabled and when the current address is equal to

the calculated end address of the buffer.