5 serial clock phase (sph), 5serial clock phase (sph) -178 – Intel STRONGARM SA-1100 User Manual

Page 328

11-178

SA-1100

Developer’s Manual

Peripheral Control Module

11.12.10.5 Serial Clock Phase (SPH)

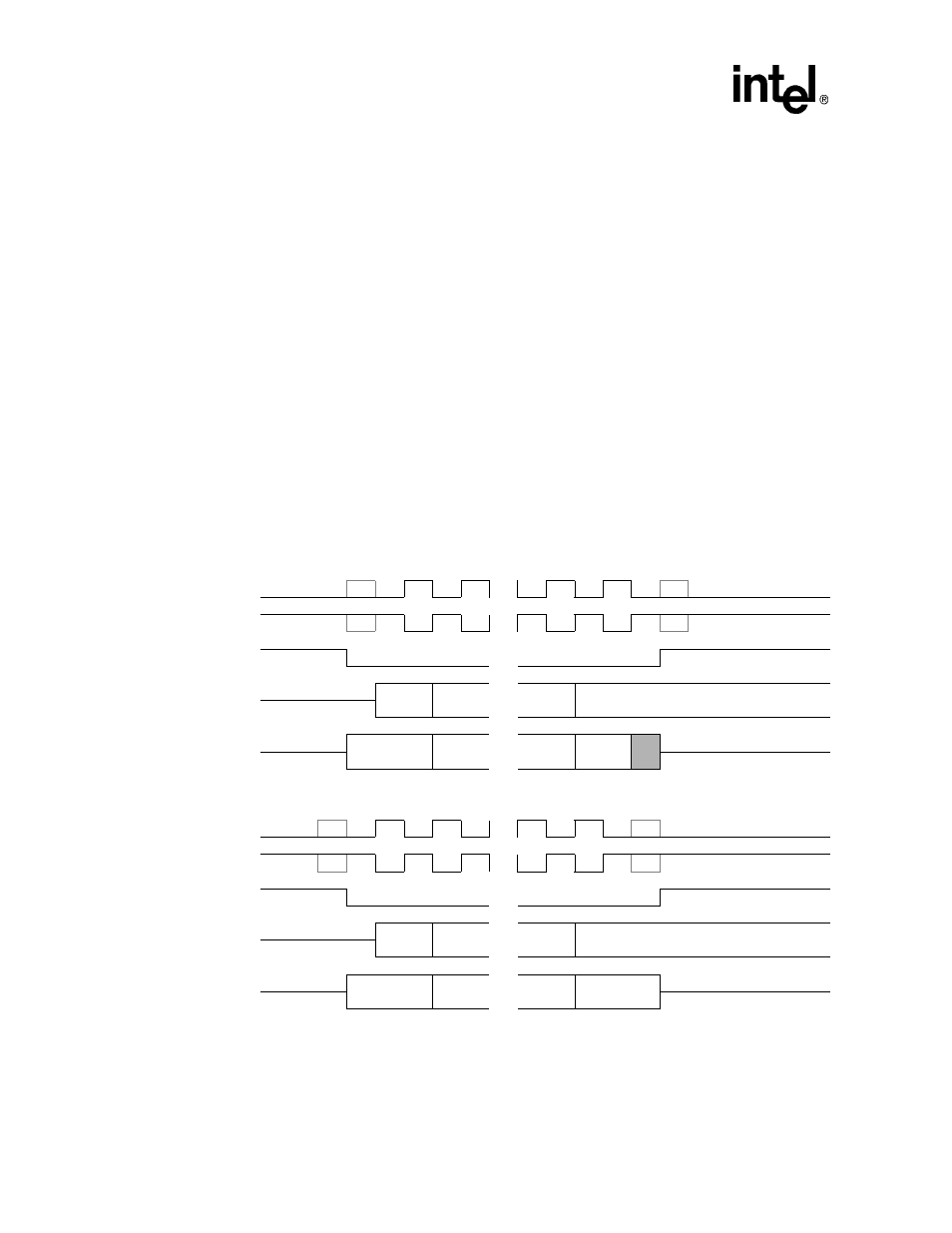

The serial clock phase (SPH) bit selects the phase relationship of the serial clock (SCLK) signal

with the serial frame (SFRM) signal when Motorola* SPI format is selected (FRF=00). When

SPH=0, SCLK remains in its inactive state (as programmed by SPO) for one full SCLK period

duration after SFRM is asserted (driven low). SCLK continues to transition during the entire frame

and is driven to its inactive state one-half SCLK period duration before SFRM is negated (driven

high). When SPH=1, SCLK remains in its inactive state (as programmed by SPO) for one-half

SCLK period duration after SFRM is asserted (driven low). SCLK continues to transition during

the entire frame and is driven to its inactive state one full SCLK period duration before SFRM is

negated (driven high). Using SPH and SPO together determine when SCLK is active during the

assertion of SFRM and which edge of SCLK is used to drive data to the transmit pin as well as

latch data from the receive pin. When SPO and SPH are the same value (both 0 or both 1), transmit

data is driven on the falling edge of SCLK and receive data is latched on the rising edge of SCLK.

Alternatively, when SPO and SPH are of opposite value (one 0 and the other 1), transmit data is

driven on the rising edge of SCLK and receive data is latched on the falling edge of SCLK. Note

that SPH is ignored in all other modes, except Motorola* SPI format (FRF=00).

shows the pin timing for all four programming combinations of SPO and SPH. Note

that SPO inverts the polarity of the SCLK signal, and SPH determines the phase relationship

between SCLK and SFRM, shifting the SCLK signal one-half phase to the left or right during the

assertion of SFRM.

Figure 11-39. Motorola

*

SPI Frame Formats for SPO and SPH Programming

SCLK

SPO=0

...

SCLK

SPO=1

...

SFRM

...

TXD4

Bit

Bit > ... Bit<1> Bit<0> RXD4 Bit Bit ... Bit<1> Bit<0> MSB 4 to 16 Bits LSB SPH = 0 SCLK SPO=0 ... SCLK SPO=1 ... SFRM ... TXD4 Bit Bit ... Bit<1> Bit<0> RXD4 Bit Bit ... Bit<1> Bit<0> MSB 4 to 16 Bits LSB SPH = 1