Active mode timing -54 – Intel STRONGARM SA-1100 User Manual

Page 204

11-54

SA-1100

Developer’s Manual

Peripheral Control Module

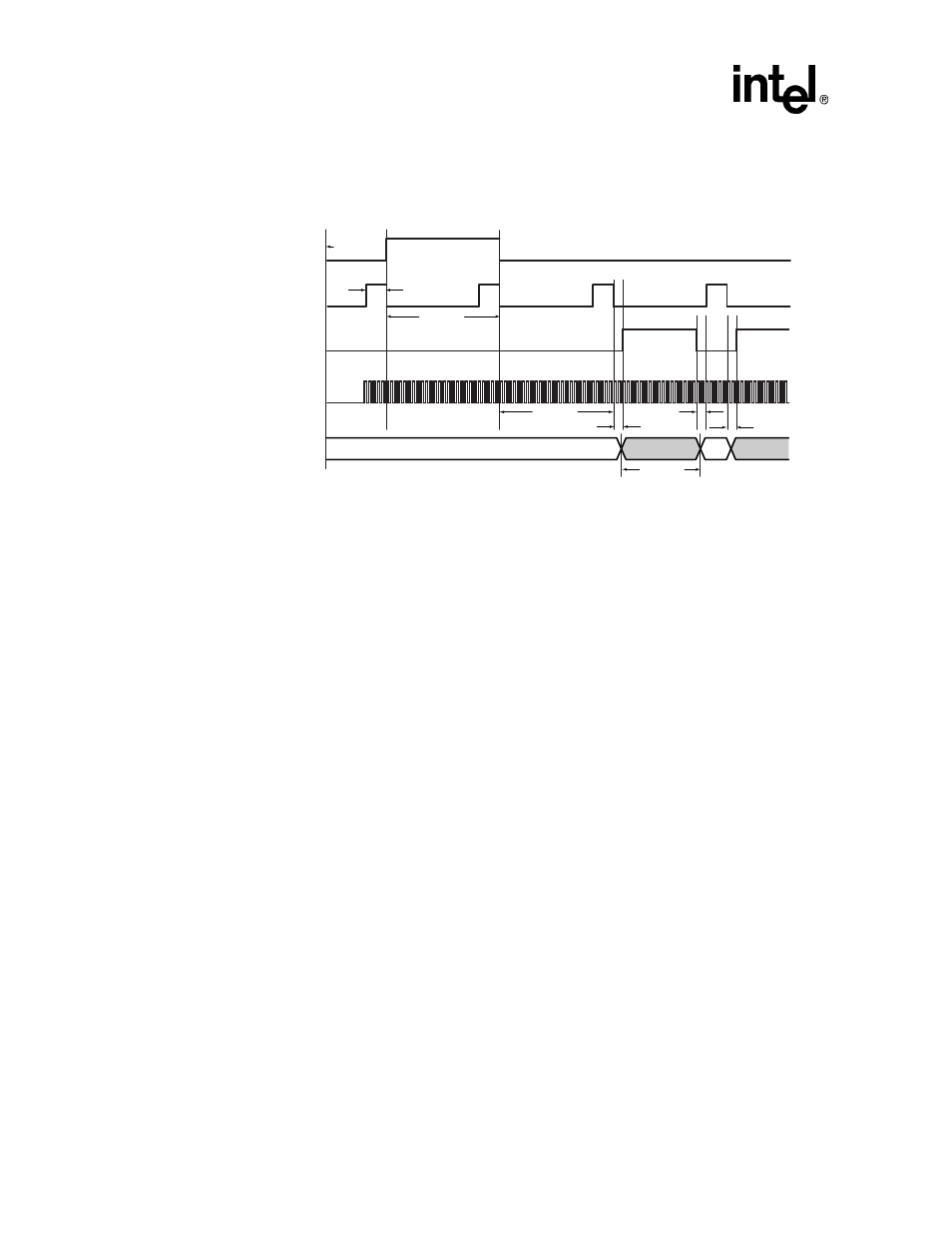

Figure 11-13. Active Mode Timing

A4793-01

L_FCLK

(VSYNC)

L_LCLK

(HSYNC)

L_BIAS

(OE)

L_PCLK

LDD[7:0],

GPIO[9:2]

Notes:

LEN - LCD enable:

0 - LCD is disabled.

1 - LCD is enabled.

VSP - Vertical sync polarity:

0 - Vertical sync clock is active high, inactive low.

1 - Vertical sync clock is active low, inactive high.

VSW - Vertical sync width:

1 to 64 horizontal sync clock periods to assert the vertical sync signal (hsync transitions).

HSW - Horizontal sync pulse width:

1 to 64 pixel clock periods to assert the line clock (pixel clock transitions).

HSP - Horizontal sync polarity:

0 - Horizontal sync clock is active high, inactive low.

1 - Horizontal sync clock is active low, inactive high.

BFW - Beginning-of-frame horizontal sync clock wait count:

0 to 255 horizontal sync clock periods to wait at the beginning of each frame (hsync transitions).

BLW - Beginning-of-line pixel clock wait count:

1 to 256 pixel clock periods to wait after line clock negated before asserting pixel clocks

(pixel clock transitions).

ELW - End-of-line pixel clock wait count:

1 to 256 pixel clock periods to wait after last pixel in line before asserting line clock (pixel clock

transitions).

PPL - Pixels per line:

1 to 1024 pixels per line on screen.

Line 1 Data

Line 0 Data

PPL = 16

HSP = 0

VSP = 0

VSW = 0

BFW = 1

ELW = 1

BFW = 2

BLW = 1

HSW = 4

LEN set to 1