Clocks 8, 1 sa-1100 crystal oscillators, Clocks – Intel STRONGARM SA-1100 User Manual

Page 67: Sa-1100 crystal oscillators -1

SA-1100 Developer’s Manual

8-1

Clocks

8

This section describes the Intel

®

StrongARM

®

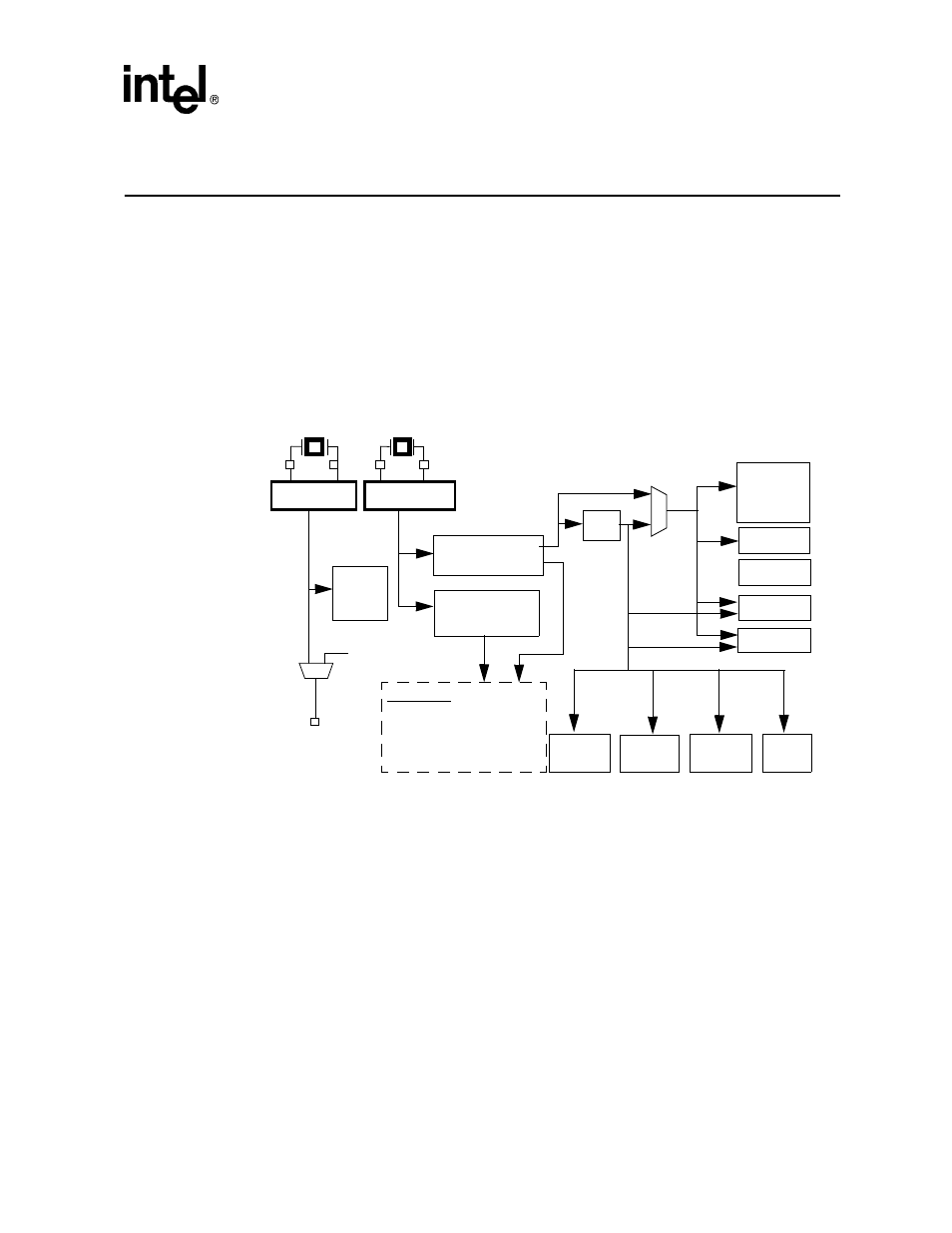

SA-1100 Microprocessor (SA-1100) clocks. The

following diagram shows the distribution of clocks in the SA-1100. The 3.6864-MHz oscillator

feeds both PLLs. The primary PLL provides clocks for the core logic and a 7.36-MHz clock for

several of the serial controllers. The core, Dcaches, and read and write buffers use either the

full-speed core clock or the divided-down clock. The LCD controller, DMA, memory controller,

and GPIO use the core clock divided by 2 (RCLK). The 32.768-kHz oscillator feeds the real-time

clock (RTC) and the power manager logic. The secondary PLL provides the clock for the UDC, the

ICP, and the MCP. The oscillators and PLLs are completely integrated with the SA-1100 and

require no external devices other than the crystals for operation.

8.1

SA-1100 Crystal Oscillators

The SA-1100 clocks are derived from two crystals connected to onchip oscillators. The first clock

source is a 3.6864-MHz crystal that feeds the CPU PLL and the 48-MHz PLL. The CPU PLL

multiplies the oscillator output up to the core frequency. This frequency is then divided down to

generate baud rates for the serial ports. If the UARTs are not being used or do not need standard

baud rates, then the 3.6864 -Hz oscillator may be replaced with a 3.5795-MHz crystal to generate

frequencies as shown in

.

The second oscillator is connected to a 32.768-kHz crystal. The output of this oscillator clocks the

power management controller and the real-time clock (RTC).

See

Appendix B, “3.6864–MHz Oscillator Specifications”

for detailed specifications of the crystal oscillators.

32.768-kHz

Oscillator

3.6864-MHz

Oscillator

Primary PLL

59 MHz – 200 MHz

Secondary PLL

48 MHz

ARM™

Icache

Dcache

Write

Buffer

Read

Buffer

I/O

Control

Memory

Controller

DMA

Controller

LCD

Controller

Divide

by 2

GPIO<27>

Peripherals

SDLC UART – 7.36 MHz

ICP – 7.36 or 48 MHz

MCP/SSP – 7.36 or 12 MHz

PPC – 7.36 MHz

UDC – 48 MHz

7.36 MHz

RTC

and

Power

Manager

SA-1 Core