Intel STRONGARM SA-1100 User Manual

Page 33

SA-1100 Developer’s Manual

2-5

Functional Description

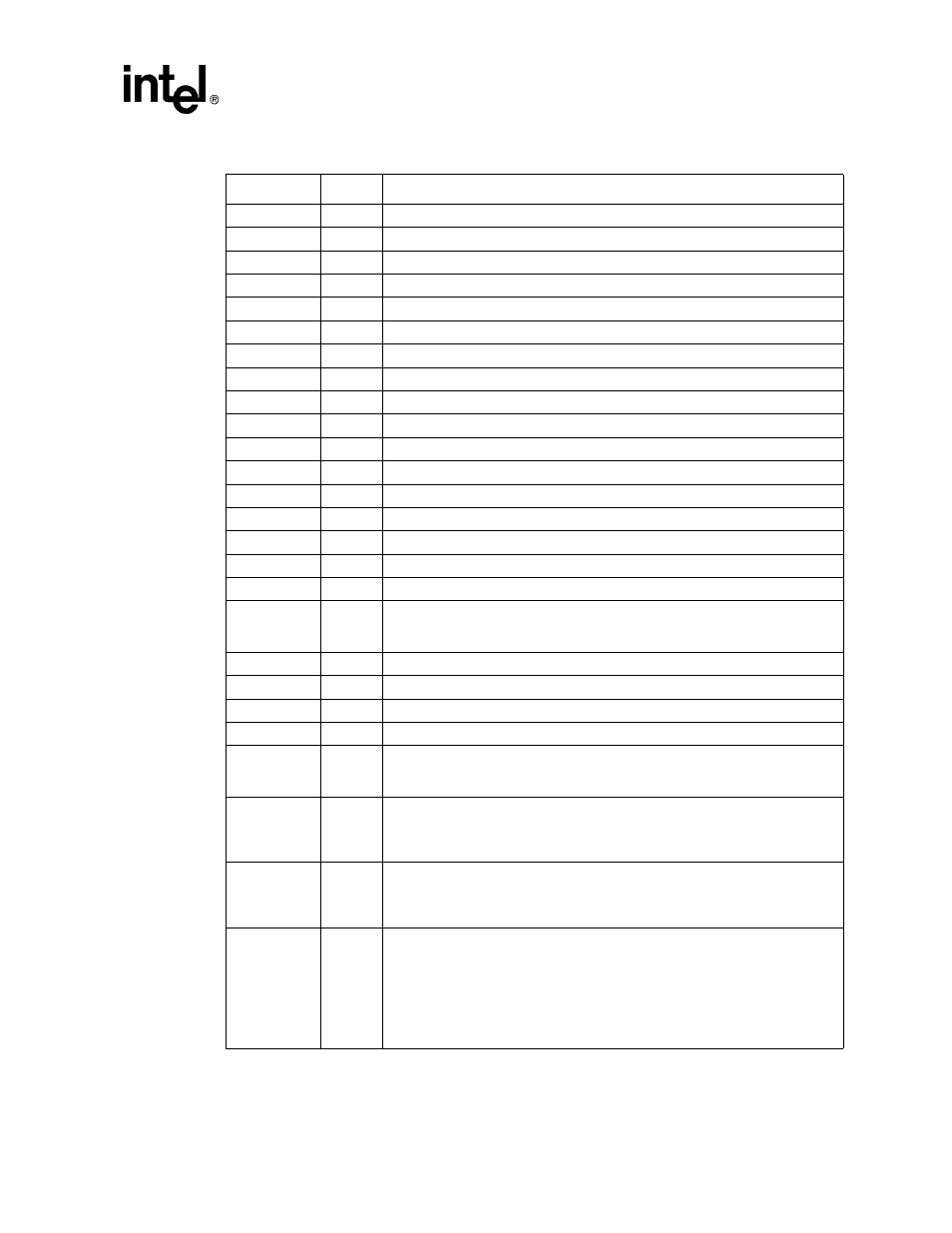

L_FCLK

OCZ

LCD frame clock.

L_LCLK

OCZ

LCD line clock.

L_PCLK

OCZ

LCD pixel clock.

L_BIAS

OCZ

LCD ac bias drive.

TXD_C

OCZ

CODEC transmit.

RXD_C

IC

CODEC receive.

SCLK_C

OCZ

CODEC clock.

SFRM_C

OCZ

CODEC frame signal.

UDC+

OCZ

Serial port zero transmit pin (UDC).

UDC-

IC

Serial port zero receive pin (UDC).

TXD_1

OCZ

Serial port one transmit pin (SDLC).

RXD_1

IC

Serial port one receive pin (SDLC).

TXD_2

OCZ

Serial port two transmit pin (IrDA).

RXD_2

IC

Serial port two receive pin (IrDA).

TXD_3

OCZ

Serial port three transmit pin (UART).

RXD_3

IC

Serial port three receive pin (UART).

GP<27:0>

ICOCZ

General-purpose input output.

ROM_SEL

IC

ROM select. This pin is used to configure the ROM width. It is either grounded or

pulled high. If ROM_SEL is grounded, the ROM width is 16 bits. If ROM_SEL is

pulled up, the ROM width is 32 bits.

PXTAL

IC

Input connection for 3.686-MHz crystal.

PEXTAL

OCZ

Output connection for 3.686-MHz crystal.

TXTAL

IC

Input connection for 32.768-kHz crystal.

TEXTAL

OCZ

Output connection for 32.768-kHz crystal.

PWR_EN

OCZ

Power enable. Active high. PWR_EN enables the external power supply.

Negating it signals the power supply that the system is going into sleep mode and

that the VDD power supply should be removed.

BATT_FAULT

IC

Battery fault. Signals the SA-1100 that the main power source is going away

(battery is low or has been removed from the system). The assertion of

BATT_FAULT causes the SA-1100 to enter sleep mode. The SA-1100 will not

recognize a wake-up event while this signal is asserted.

VDD_FAULT

IC

VDD fault. Signals the SA-1100 that the main power supply is going out of

regulation (shorted card is inserted). VDD_FAULT will cause the SA-1100 to enter

sleep mode. VDD_FAULT is ignored after a wake-up event until the poser supply

timer completes (approximately 10 ms).

nRESET

IC

Hard reset. This active low signal is a level-sensitive input used to start the

processor from a known address. A low level will cause the current instruction to

terminate abnormally, and the on-chip caches, MMU, and write buffer to be

disabled.

When nRESET is driven high, the processor will restart from address 0. nRESET

must remain low until the power supply is stable and the internal 3.686-MHz

oscillator has come up to speed. While nRESET is low, the processor will perform

idle cycles.

Table 2-1.

Signal Descriptions (Sheet 2 of 3)

Name

Type

Description