10 register 9 – read-buffer operations, 11 registers 10 – 12 reserved, 10 register 9 – read-buffer operations -6 – Intel STRONGARM SA-1100 User Manual

Page 50: 11 registers 10 – 12 reserved -6

5-6

SA-1100

Developer’s Manual

Coprocessors

5.2.10

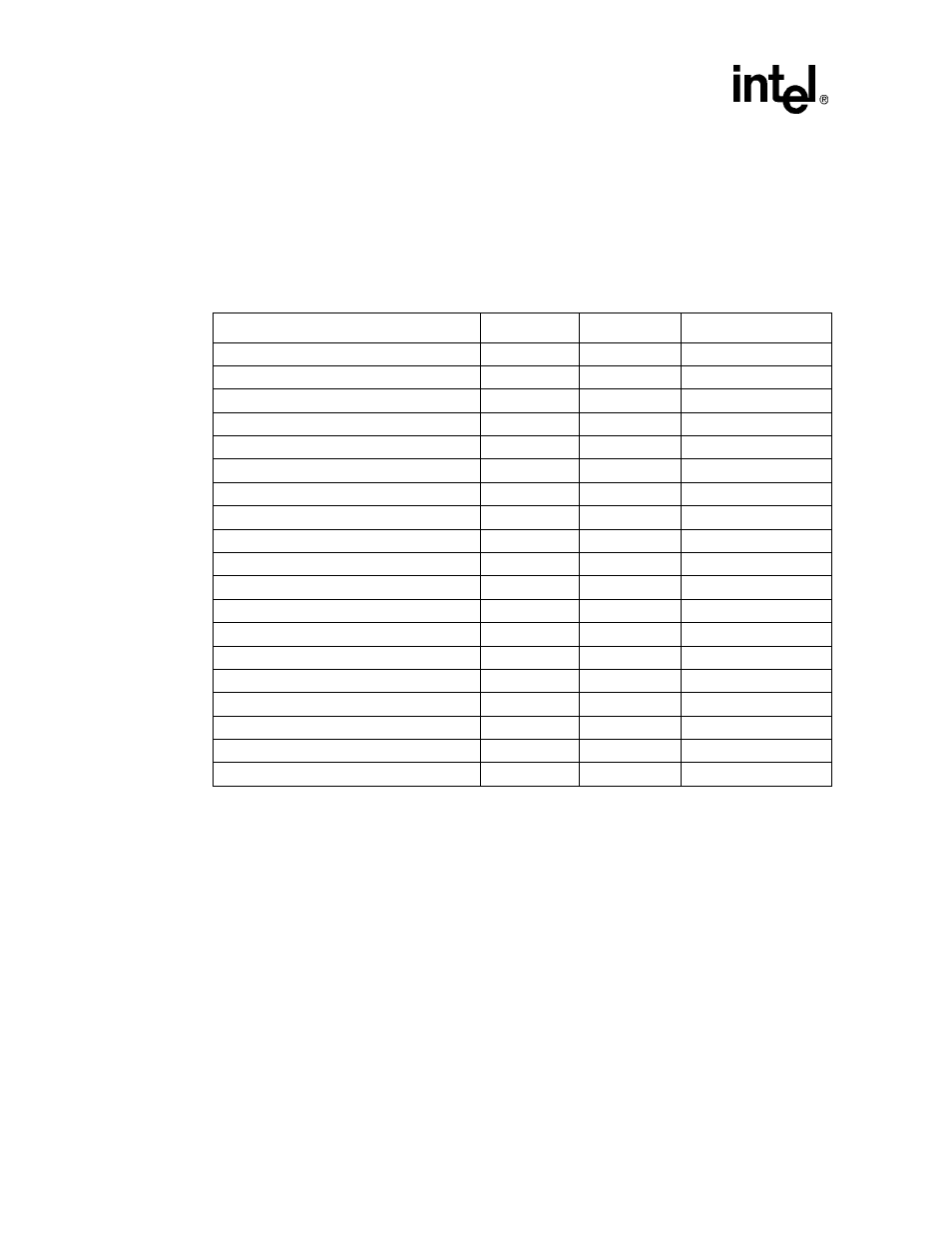

Register 9 – Read-Buffer Operations

The read buffer is controlled and accessed through register 9 of coprocessor 15. The functions

supported are: flush-all buffers, flush-a-single entry, load-an-entry (1, 4 or 8 words), and

enable/disable user mode access.

The CRm and OPC_2 fields are used to encode these control operations. All other values for

OPC_2 and CRm are undefined and the results of using them are unpredictable.

See

Chapter 6, “Caches, Write Buffer, and Read Buffer”

for details on the use and operation of the

read buffer.

5.2.11

Registers 10 – 12 RESERVED

Accessing any of these registers yields unpredictable results.

Function

OPC_2

CRm

Data

Flush all entries

0b000

0b0000

Ignored

Flush Buffer 0

0b001

0b0000

Ignored

Flush Buffer 1

0b001

0b0001

Ignored

Flush Buffer 2

0b001

0b0010

Ignored

Flush Buffer 3

0b001

0b0011

Ignored

Load Buffer 0 with one word

0b010

0b0000

Virtual address

Load Buffer 0 with four words

0b010

0b0100

Virtual address

Load Buffer 0 with eight words

0b010

0b1000

Virtual address

Load Buffer 1 with one word

0b010

0b0001

Virtual address

Load Buffer 1 with four words

0b010

0b0101

Virtual address

Load Buffer 1 with eight words

0b010

0b1001

Virtual address

Load Buffer 2 with one word

0b010

0b0010

Virtual address

Load Buffer 2 with four words

0b010

0b0110

Virtual address

Load Buffer 2 with eight words

0b010

0b1010

Virtual address

Load Buffer 3 with one word

0b010

0b0011

Virtual address

Load Buffer 3 with four words

0b010

0b0111

Virtual address

Load Buffer 3 with eight words

0b010

0b1011

Virtual address

Disable user-mode MCR access

0b100

0b0000

Ignored

Enable user-mode MCR access

0b101

0b0000

Ignored