1 signalling levels, 1signalling levels -57, Usb bus states -57 – Intel STRONGARM SA-1100 User Manual

Page 207

SA-1100 Developer’s Manual

11-57

Peripheral Control Module

11.8.1.1

Signalling Levels

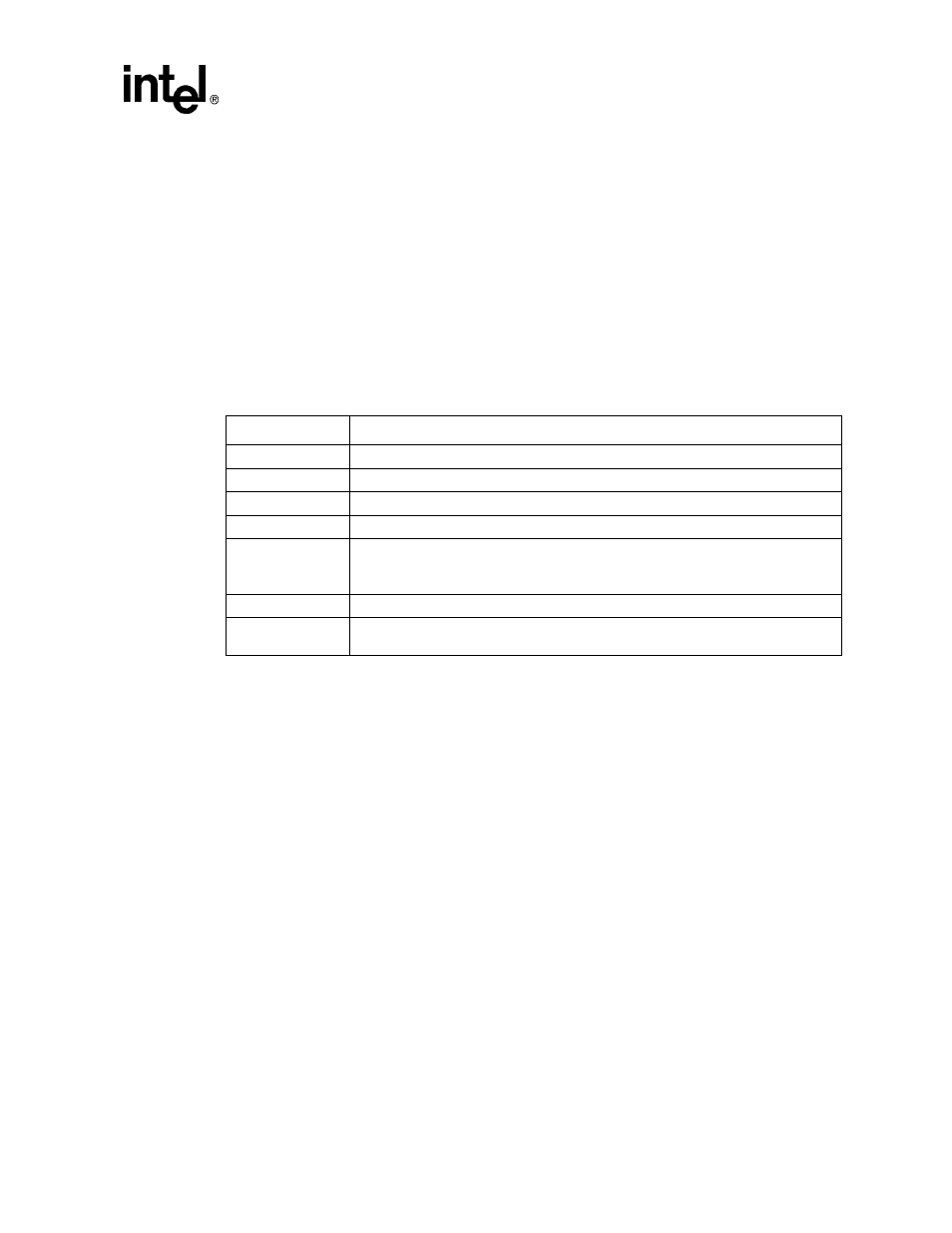

USB uses differential signalling to encode data and to communicate various bus conditions. The

USB specification refers to the J and K data states to differentiate between high- and low-speed

transmission. Because the UDC supports only 12-Mbps transmission, references are made only to

actual data state 0 and actual data state 1.

Four distinct states are represented using differential data by decoding the polarity of the UDC+

and UDC- pins. Two of the four states are used to represent data. A one is represented when UDC+

is high and UDC- is low; a zero is represented when UDC+ is low and UDC- is high. The

remaining two states and pairings of the four encodings are further decoded to represent the current

state of the USB bus.

shows how seven different bus states are represented using

differential signalling.

Hosts and hubs have pull-down resistors on both the D+ and D- lines. When a device is not attached

to the cable, the pull-down resistors cause D+ and D- to be pulled down below the single-ended low

threshold of the host or hub. This creates a state called single-ended zero (SE0). A disconnect is

detected by the host when an SE0 persists for more than 2.5 µs (30-bit times). When the UDC is

connected to the USB cable, the pull-up resistor on the UDC+ pin causes D+ to be pulled above the

single-ended high threshold level. After 2.5 µs elapse, the host detects a connect.

After this point, the bus is in the idle state because UDC+ is high and UDC- is low. A start of

packet is signalled by transitioning the bus from the idle to the resume state (a 1 to 0 transition).

The beginning of each USB packet begins with a sync field, which starts with the 1-to-0 transition

(see the

Section 11.8.1.1, “Signalling Levels” on page 11-57

). After the packet data has been

transferred, an end of packet is signalled by pulling both UDC+ and UDC- low for 2-bit times,

followed by an idle for 1-bit time. If the idle persists for more than 3 ms, the UDC enters suspend

mode and it is placed in low-power mode. The UDC can be awakened from the suspend state by

the host by switching the bus to the resume state via normal bus activity, or by signalling a reset.

Under normal operating conditions, the host ensures that devices do not enter the suspend state by

periodically signalling an end of packet (EOP).

Table

11-10. USB

Bus

States

Bus State

UDC+/UDC- Pin Levels

Idle

UDC+ high, UDC- low (same as a 1).

Resume

UDC+ low, UDC- high (same as a 0).

Start of Packet

Transition from idle to resume.

End of Packet

UDC+ AND UDC- low for 2-bit times followed by an idle for 1-bit time.

Disconnect

UDC+ AND UDC- below single-ended low threshold for more than 2.5 µs.

(Disconnect is the static bus condition that results when no device is plugged into a hub

port.)

Connect

UDC+ OR UDC- high for more than 2.5 µs.

Reset

UDC+ AND UDC- low for more than 2.5 µs. (Reset is driven by the host controller and

sensed by a device controller.)