Dram burst-of-eight transactions -17 – Intel STRONGARM SA-1100 User Manual

Page 131

SA-1100 Developer’s Manual

10-17

Memory and PCMCIA Control Module

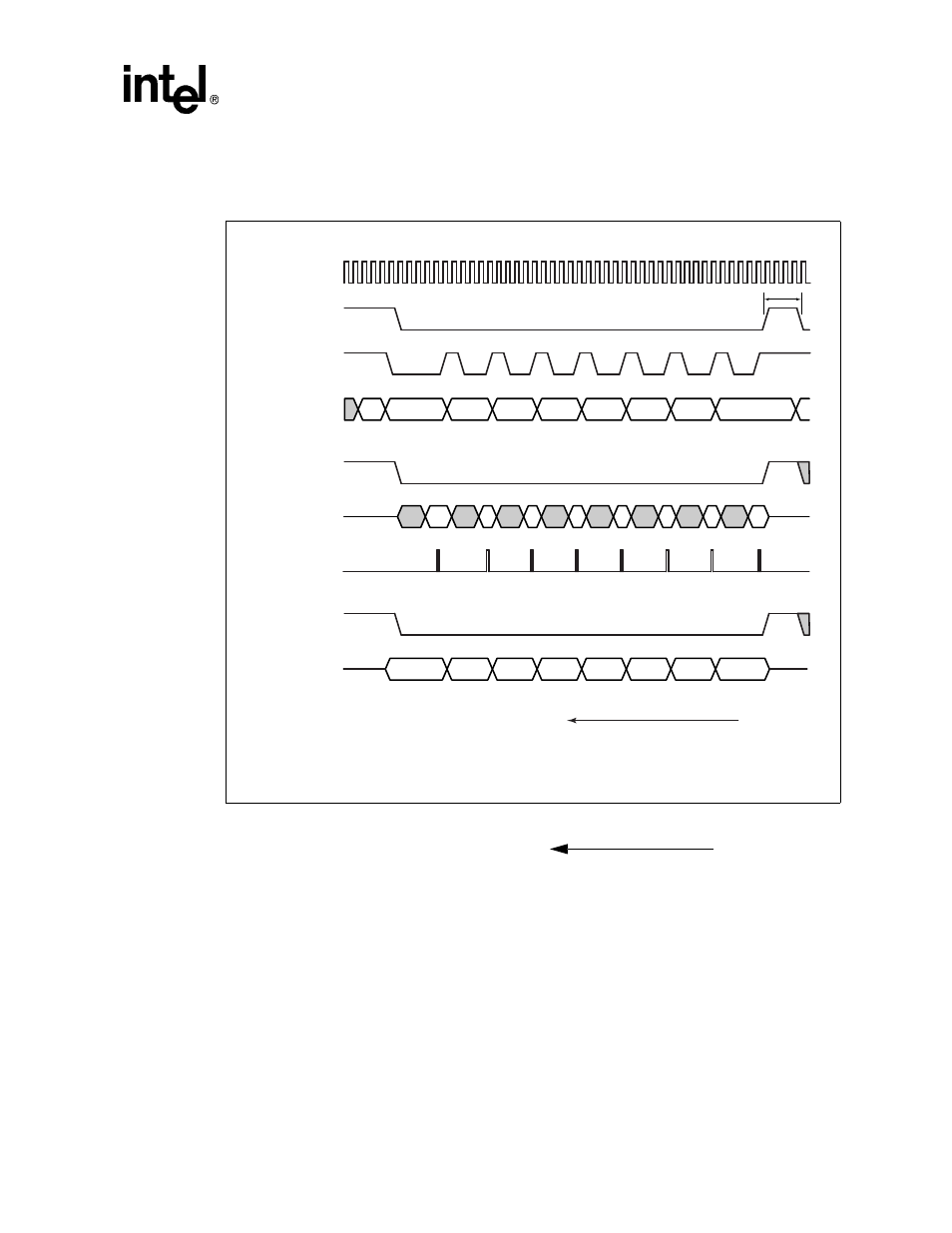

shows the rate of the shift registers during DRAM nCAS timing for burst-of-eight

transactions.

Figure 10-4. DRAM Burst-of-Eight Transactions

A4778-01

Memory Clock

ADDR

Input Data

Latch Input Data (internal):

Reads:

TRP

nRAS

nOE

Writes:

Write Data

nWE

nCAS

COL

D0

D1

D2

D3

D4

D5

D6

D7

COL+4 COL+8 COL+12 COL+16 COL+20 COL+24

COL+28

D0

D1

D2

D3

D4

D5

D6

D7

ROW

Contents of DRAM register fields:

MDCAS1 = 11 0001 1000 1100 (binary) MDCAS0 = 0110 0011 0001 1000 1100 0110 0000 0111 (binary)

first

last

time

MDCNFG:TRP = 4 MDCNFG:CDB2 = 1 TDL = 00

Contents of DRAM register fields:

MDCNFG:TRP=4

MDCAS0= 0110 0011 0001 1000 1100 0110 0000 0111(binary)

MDCAS1=11 0001 1000 1100(binary)

MDCNFG:CDB2=1 TDL=00

time

first

last

See also other documents in the category Intel Hardware:

- 41210 (64 pages)

- 8xC251TQ (20 pages)

- ENTERPRISE PRINTING SYSTEM (EPS) 4127 (84 pages)

- U3-1L (20 pages)

- 80960HA (104 pages)

- X58 (54 pages)

- ESM-2850 2047285001R (91 pages)

- ATOM US15W (54 pages)

- D915GVWB (4 pages)

- XP-P5CM-GL (28 pages)

- AX965Q (81 pages)

- CORETM 2 DUO MOBILE 320028-001 (42 pages)

- CV700A (63 pages)

- 80C188EA (50 pages)

- X25-M (28 pages)

- XP-P5IM800GV (26 pages)

- IB868 (60 pages)

- D865GVHZ (88 pages)

- IB865 (64 pages)

- Altera P0424-ND (1 page)

- 8086-2 (30 pages)

- IXDP465 (22 pages)

- IWILL P4D (104 pages)

- GA-8I955X PRO (88 pages)

- FSB400 (PC2100) (96 pages)

- D845GLAD (4 pages)

- NAR-3041 (1 page)

- 87C196CA (136 pages)

- G52-M6734XD (74 pages)

- A96134-002 (10 pages)

- Express Routers 9000 (8 pages)

- 82540EP (45 pages)

- D865GLC (94 pages)

- IB850 (69 pages)

- MB898RF (62 pages)

- Arima LH500 (78 pages)

- V09 (33 pages)

- I/O Processor (22 pages)

- M600 (110 pages)

- SE7520JR2 (63 pages)

- SERVER BOARD S5520HCT (30 pages)

- Extensible Firmware Interface (1084 pages)

- GA-8IPXDR-E (70 pages)

- D845EBG2 (4 pages)

- AW8D (80 pages)