1 gpio pin-level register (gplr), 1 gpio pin-level register (gplr) -3, System control module – Intel STRONGARM SA-1100 User Manual

Page 73

SA-1100 Developer’s Manual

9-3

System Control Module

9.1.1.1

GPIO Pin-Level Register (GPLR)

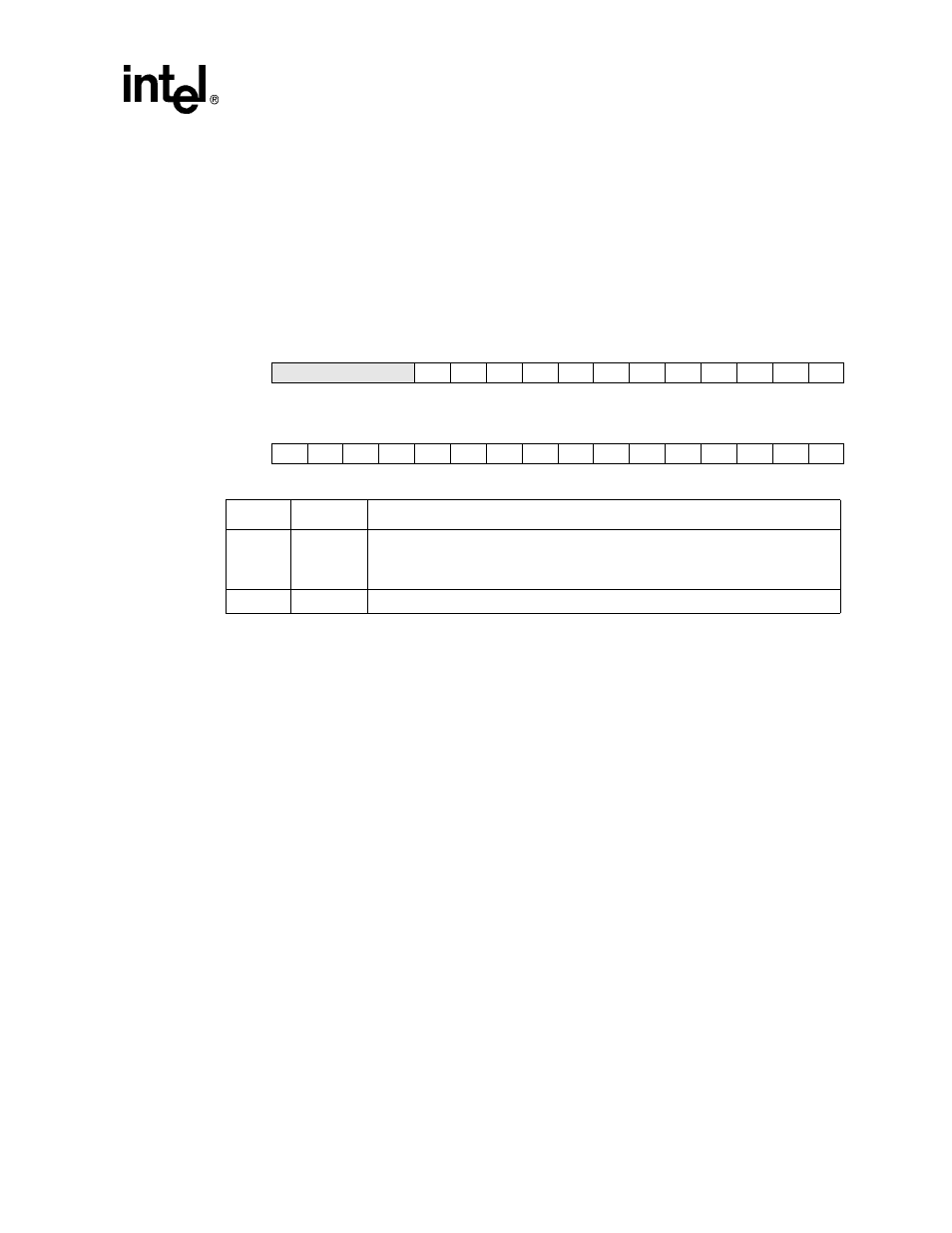

The state of each of the GPIO port pins is visible through the GPIO pin-level register (GPLR).

Each bit number corresponds to the port pin number from bit 0 to bit 27. This is a read-only register

that is used to determine the current level of a particular pin (regardless of the programmed pin

direction).

The following table shows the locations of the 28 pin-level bits within the GPLR. This is a

read-only register. For reserved bits, reads return zero; a question mark indicates that the values are

unknown at reset.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Read

Reserved

PL27

PL26

PL25

PL24

PL23

PL22

PL21

PL20

PL19

PL18

PL17

PL16

Reset

0

0

0

0

?

?

?

?

?

?

?

?

?

?

?

?

-

-

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Read

PL15

PL14

PL13

PL12

PL11

PL10

PL9

PL8

PL7

PL6

PL5

PL4

PL3

PL2

PL1

PL0

Reset

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

Bit

Name

Description

{n}

PL{n}

GPIO port pin level n (where n = 0 through 27).

0 – Pin state is low.

1 – Pin state is high.

31.. 28

—

Reserved.