Intel STRONGARM SA-1100 User Manual

Page 199

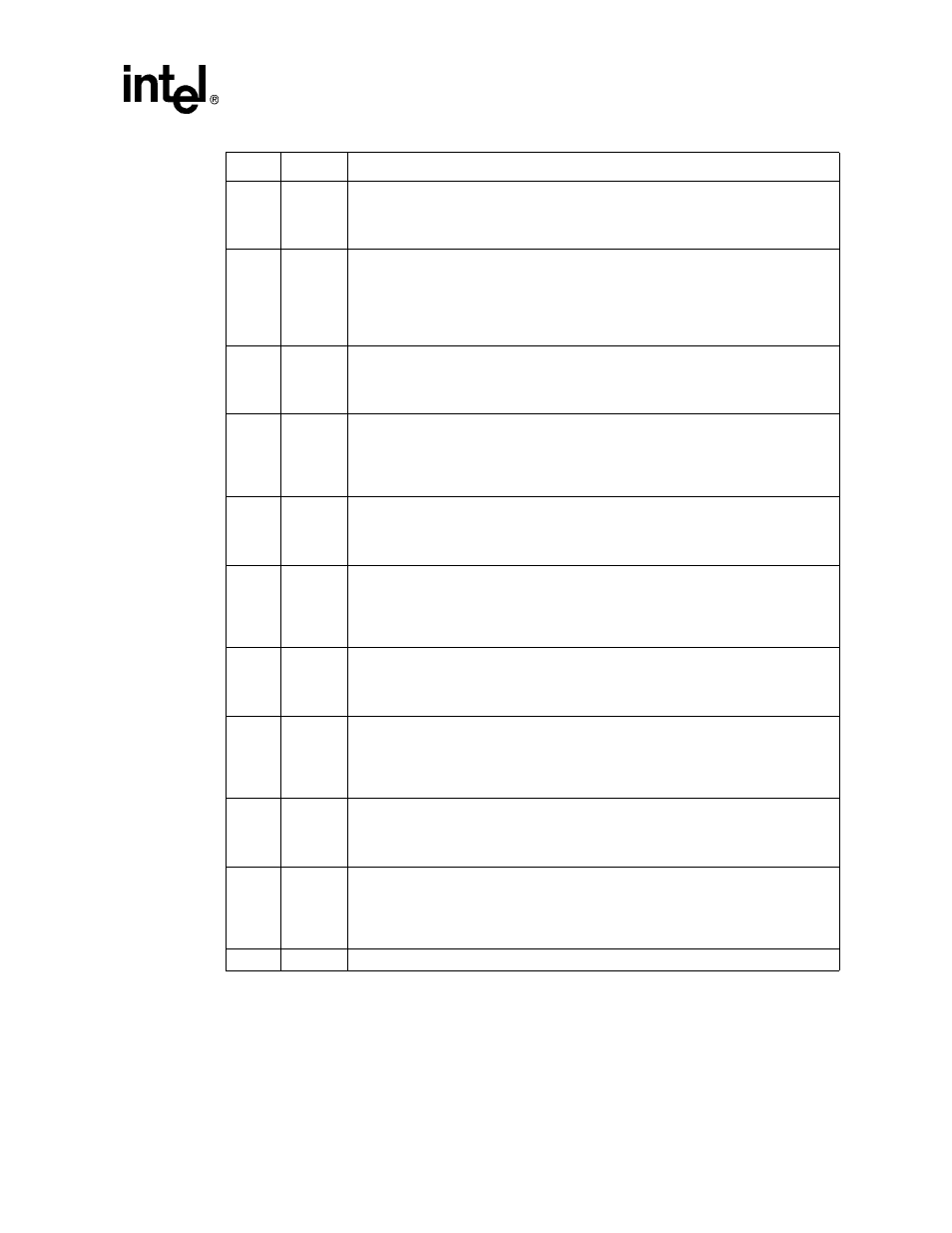

SA-1100 Developer’s Manual

11-49

Peripheral Control Module

2

BER

Bus error status.

0 – DMA has not attempted an access to reserved/nonexistent memory space.

1 – DMA has attempted an access to a reserved/nonexistent location in external

memory. The errant DMA read returns zeros.

3

ABC

AC bias count status.

0 – AC bias transition counter has not decremented to zero, or API is programmed to all

zeros.

1 – AC bias transition counter has decremented to zero, indicating that the L_BIAS pin

has transitioned the number of times specified by the API control bit field. Counter is

reloaded with the value in API but is disabled until the user clears ABC.

4

IOL

Input FIFO overrun lower panel status.

0 – Input FIFO for the lower panel display has not overrun.

1 – DMA attempted to place data into the input FIFO for the lower panel after it has been

filled.

5

IUL

Input FIFO underrun lower panel status.

0 – Input FIFO for the lower panel display has not underrun.

1 – DMA not supplying data to input FIFO for the lower panel at a sufficient rate. FIFO

has completely emptied; pixel unpacking logic has attempted to take added data from

the FIFO.

6

IOU

Input FIFO overrun upper panel status.

0 - Input FIFO for the upper or whole panel display has not overrun.

1 - DMA attempted to place data into the input FIFO for the upper or whole panel after it

has been filled.

7

IUU

Input FIFO underrun upper panel status.

0 – Input FIFO for the upper or whole panel display has not underrun.

1 – DMA not supplying data to input FIFO for the upper or whole panel at a sufficient

rate. FIFO has completely emptied; pixel unpacking logic has attempted to take added

data from the FIFO.

8

OOL

Output FIFO overrun lower panel status.

0 – Output FIFO for the lower panel display has not overrun.

1 – Dither logic attempted to place data into the output FIFO for the lower panel after it

had been filled.

9

OUL

Output FIFO underrun lower panel status.

0 – Output FIFO for the lower panel display has not underrun.

1 – LCD dither logic not supplying data to output FIFO for the lower panel at a sufficient

rate. FIFO has completely emptied and data pin driver logic has attempted to take

added data from the FIFO.

10

OOU

Output FIFO overrun upper panel status.

0 – Output FIFO for the upper or whole panel display has not overrun.

1 – Dither logic attempted to place data into the output FIFO for the upper or whole

panel after it had been filled.

11

OUU

Output FIFO underrun upper panel status.

0 – Output FIFO for the upper or whole panel display has not underrun.

1 – LCD dither logic not supplying data to output FIFO for the upper or whole panel at a

sufficient rate. FIFO has completely emptied and data pin driver logic has attempted to

take added data from the FIFO.

31..12

—

Reserved.

Bit

Name

Description