Intel STRONGARM SA-1100 User Manual

Page 251

SA-1100 Developer’s Manual

11-101

Peripheral Control Module

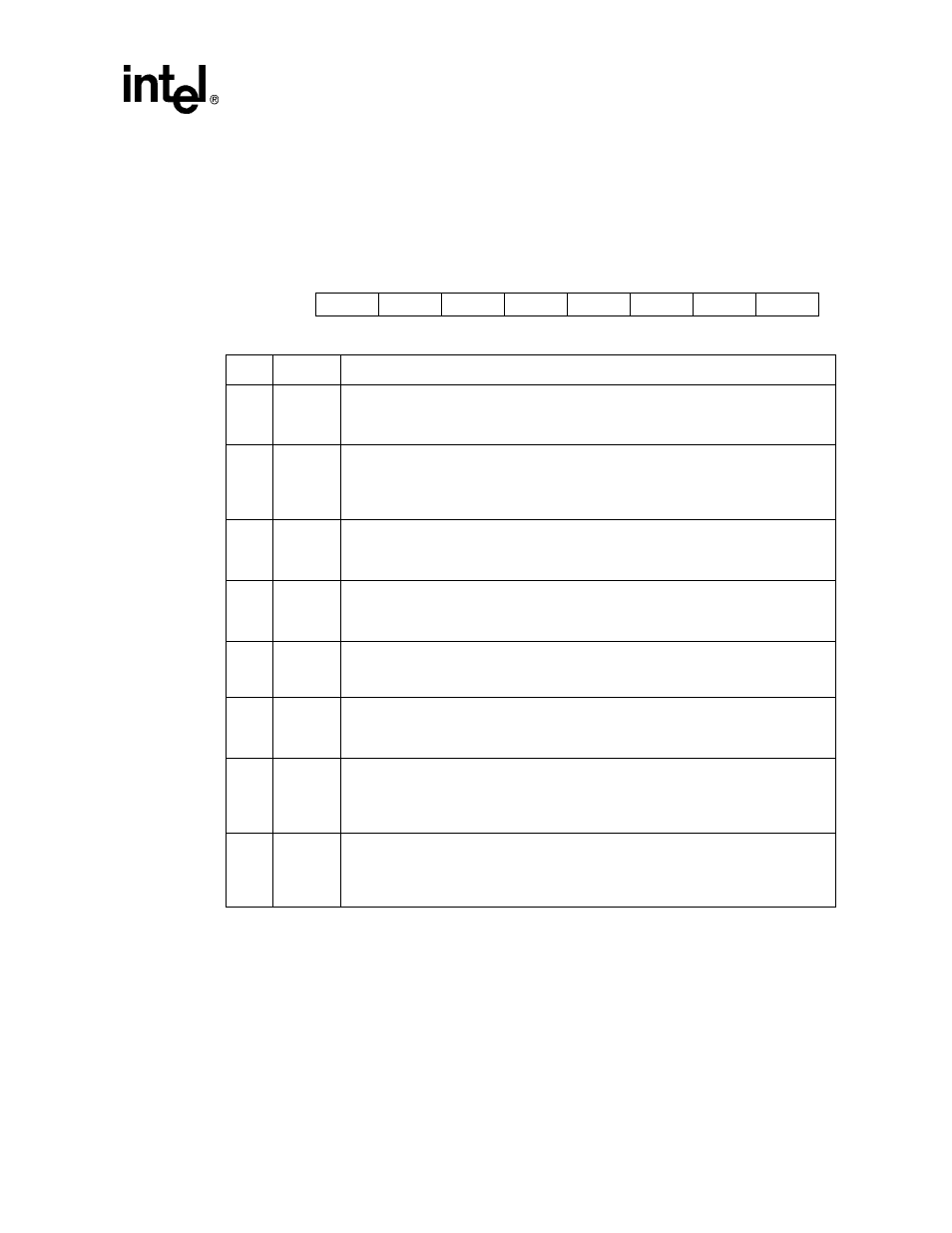

The following table shows the location of the flag and status bits within SDLC status register 1.

The bits within this register do not produce interrupt requests. Note that the reset value of RTD is

unknown (indicated by question marks) and must be cleared if set following a reset of the

SA-1100. The remainder of SDSR1 is read-only (writes are ignored).

.

Address: 0h 8002 0084

SDSR1

Read/Write & Read-Only

Bit

7

6

5

4

3

2

1

0

ROR

CRE

EOF

RTD

TNF

RNE

TBY

RSY

Reset

0

0

0

?

1

0

0

0

Bit

Name

Description

0

RSY

Receiver synchronized flag (read-only).

0 – Receiver is in hunt mode or is disabled.

1 – Receiver logic is synchronized with the incoming data (no interrupt generated).

1

TBY

Transmitter busy flag (read-only).

0 – Transmitter is idle (continuous flags) or disabled.

1– Transmit logic is currently transmitting a frame (address, control, data, CRC, or

start/stop flag) or an abort (no interrupt generated).

2

RNE

Receive FIFO not empty (read-only).

0 – Receive FIFO is empty.

1 – Receive FIFO is not empty (no interrupt generated).

3

TNF

Transmit FIFO not full (read-only).

0 – Transmit FIFO is full.

1 – Transmit FIFO is not full (no interrupt generated).

4

RTD

Receive transition detect.

0 – No transition detected on RXD1 pin since the last time software cleared this bit.

1 – Rising and/or falling edge detected on RXD1 pin (no interrupt generated).

5

EOF

End of frame (read-only).

0 – Current frame has not completed.

1 – The value at the bottom of the receive FIFO is the last byte of data within the frame.

6

CRE

CRC error (read-only).

0 – No CRC check errors encountered in the receipt of data.

1 – CRC calculated on the incoming data does not match CRC value contained within

the received frame.

7

ROR

Receive FIFO overrun (read-only).

0 – Receive FIFO has not experienced an overrun.

1 – Receive logic attempted to place data into receive FIFO while it was full; the next

data value in the FIFO is the last piece of “good” data before the FIFO was overrun.