2 reset controller status register (rcsr), 2 reset controller register locations, 2 reset controller status register (rcsr) -43 – Intel STRONGARM SA-1100 User Manual

Page 113: Reset controller register locations -43, System control module, Hardware reset, Software reset, Watchdog reset, Table 9-5. reset controller register locations

SA-1100 Developer’s Manual

9-43

System Control Module

9.6.1.2

Reset Controller Status Register (RCSR)

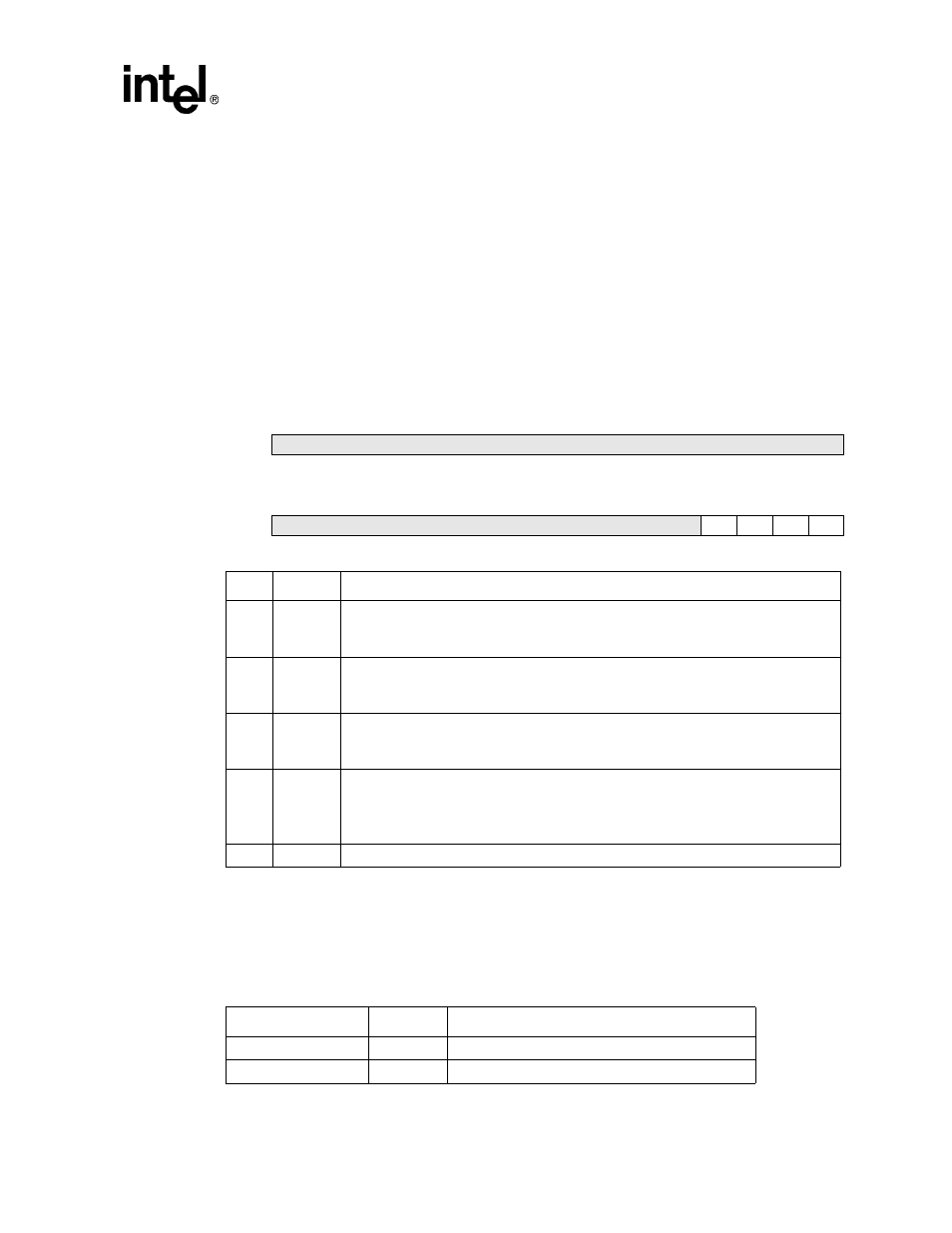

The reset controller reset status register (RCSR) is used by the CPU to determine the last cause or

causes of the reset. The SA-1100 has four sources of reset:

•

Hardware reset

•

Software reset

•

Watchdog reset

•

Sleep mode reset

Each RCSR status bit is set by a different source of reset, and can be cleared by writing a one back to that

bit. Note that the hardware reset state of software, watchdog, and sleep mode reset bits is zero. The table

below shows the status bits within RCSR. For reserved bits, writes are ignored and reads return zero.

9.6.2

Reset Controller Register Locations

shows the registers associated with the reset controller and the physical addresses used to

access them.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R/W

Reserved

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R/W

Reserved

SMR

WDR

SWR

HWR

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

Bit

Name

Description

0

HWR

Hardware reset.

0 – Hardware reset has not occurred since the last time the CPU cleared this bit.

1 – Hardware reset has occurred since the last time the CPU cleared this bit.

1

SWR

Software reset.

0 – Software reset has not occurred since the last time the CPU cleared this bit.

1 – Software reset has occurred since the last time the CPU cleared this bit.

2

WDR

Watchdog reset.

0 – Watchdog reset has not occurred since the last time the CPU cleared this bit.

1 – Watchdog reset has occurred since the last time the CPU cleared this bit.

3

SMR

Sleep mode reset.

0 – Sleep mode reset has not occurred since the last time the CPU cleared this bit.

1 – Sleep mode reset has occurred since the last time the CPU cleared this bit.

Note: Each status flag can be cleared only by reading a one and then writing a zero to it.

31..4

—

Reserved.

Table 9-5.

Reset Controller Register Locations

Address

Name

Description

0h 9003 0000

RSRR

Reset controller software reset register

0h 9003 0004

RCSR

Reset controller status register