4 rtc trim register (rttr), 5 trim procedure, 1 oscillator frequency calibration – Intel STRONGARM SA-1100 User Manual

Page 89: Rtc trim register (rttr) -19, System control module

SA-1100 Developer’s Manual

9-19

System Control Module

9.3.4

RTC Trim Register (RTTR)

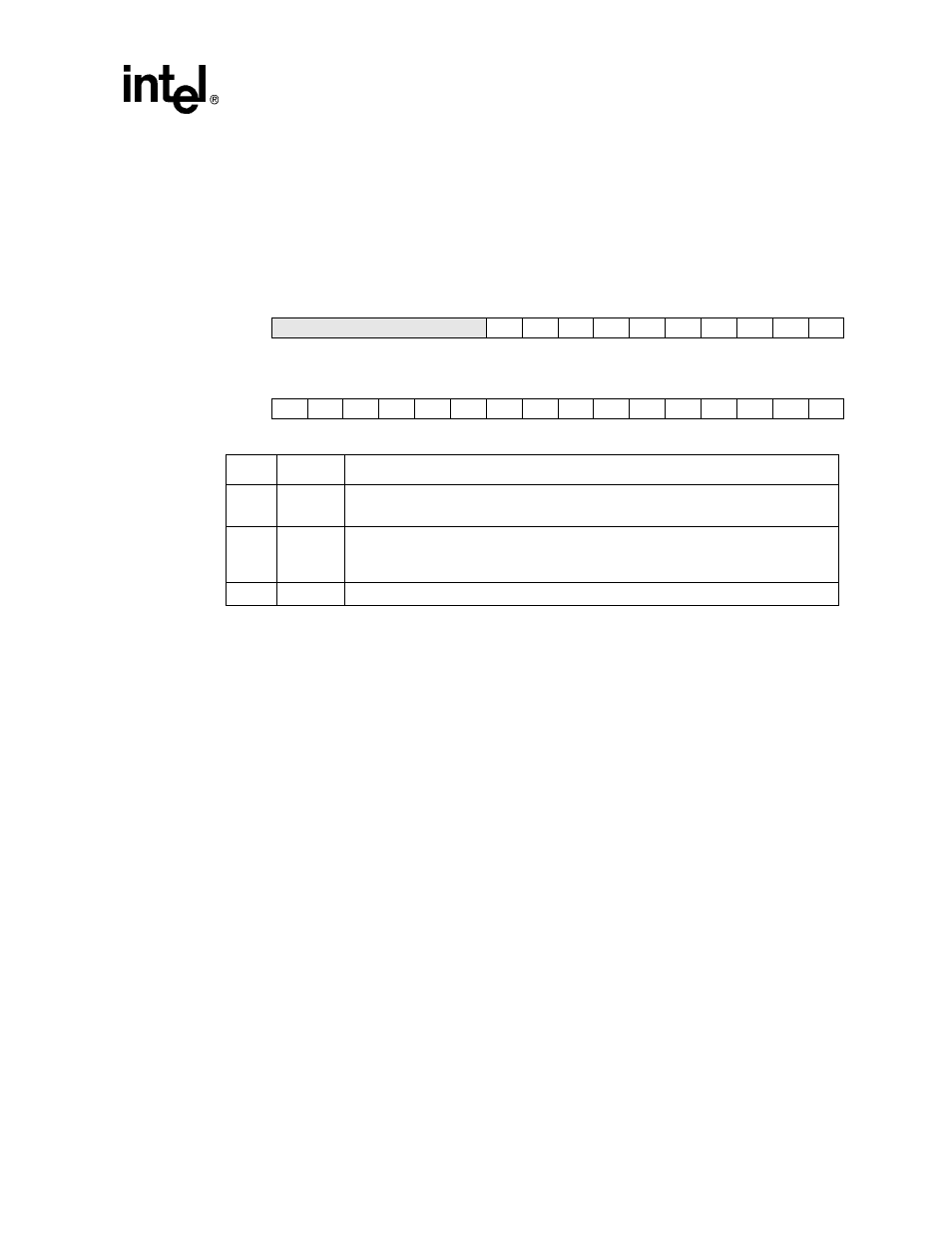

The RTTR is programmed by the user to select the frequency of the 1-Hz clock. If this register is

not programmed and left at its reset value (all zeros), then the 1-Hz clock will actually be running

at 32.768 kHz. See the following section for details on how to calculate the value in this register.

The following table shows the location of all bits in the RTTR. All reserved bits are read as zeros

and are unaffected by writes.

.

9.3.5

Trim Procedure

The 1-Hz clock feeding the RTC is obtained by dividing the output of the 32.768-kHz oscillator

down. Since 32768 is a power of two, a 15-bit divider will generate a 1-Hz clock (given a perfect

crystal and perfect board environment). The inherent inaccuracies of crystals, aggravated by

varying capacitance of the board connections, and so on, cause the timebase to be somewhat

inaccurate, requiring a periodic adjustment in the 1 Hz clock period. The SA-1100, through the

RTTR, allows the user to adjust or "trim" the 1 Hz timebase to an accuracy of +/- 5 seconds per

month. At reset, the RTTR contains zeros that disable the trim circuitry. When the trim circuitry is

disabled, the 1-Hz clock feeding the RTC is the same frequency as the output of the 32.768-kHz

oscillator. The RTTR is reset to all zeros each time the nRESET signal is asserted.

9.3.5.1

Oscillator Frequency Calibration

To generate the value to be entered into the RTTR, the user must first measure the output frequency

of the 32.768-kHz oscillator using an accurate timebase, such as a frequency counter. This clock is

made externally visible by selecting the alternate function for GPIO<27>. To gain access to the

clock, this pin must be programmed as an output and then switched over to the alternate function.

See the

Section 9.1, “General-Purpose I/O” on page 9-1

in this chapter for details on how to gain

access to the clock. The trim is accomplished by dividing the output of the oscillator by an integer

value and then doing fine-grain fractional adjustment by periodically deleting clocks from the

stream feeding this integer divider.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R/W

Reserved

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R/W

C15

C14

C13

C12

C11

C10

C9

C8

C7

C6

C5

C4

C3

C2

C1

C0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

Name

Description

0..15

C0-C15

Clock divider count.

This value is the integer portion of the clock trim logic.

16..25

D0-9

Trim delete count.

This value represents the number of 32-kHz clocks to delete when clock trimming

begins.

26..31

—

Reserved.