1 frame format, 1frame format -147, Mcp frame data format -147 – Intel STRONGARM SA-1100 User Manual

Page 297: Mcp frame pin timing -147, Peripheral control module

SA-1100 Developer’s Manual

11-147

Peripheral Control Module

11.12.1.1

Frame Format

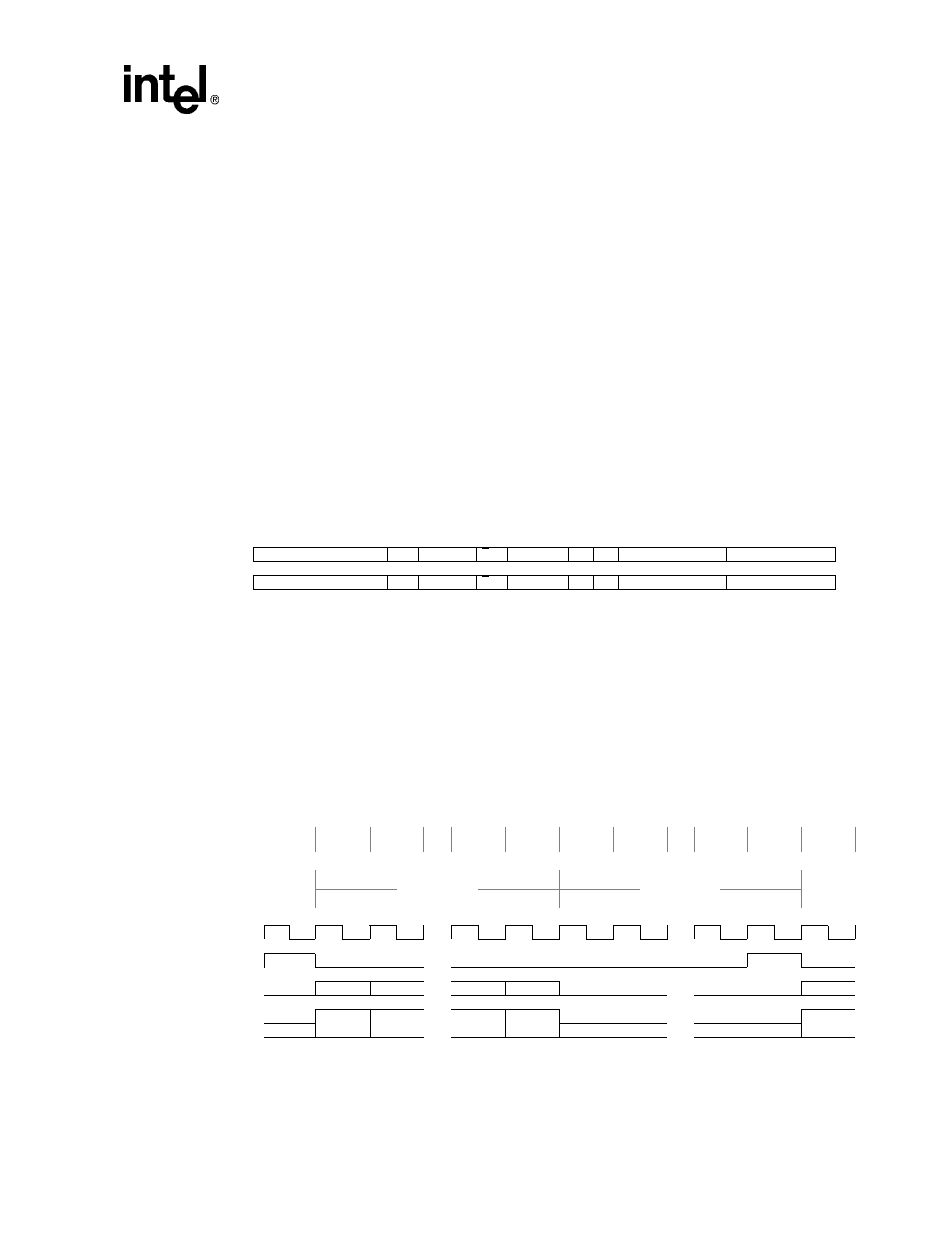

Each MCP data frame is 128 bits long and is divided into two subframes: 0 and 1. Subframe 0 is

used by the MCP to communicate data to and from the UCB1100 or UCB1200. Subframe 1 is not

used by the MCP because it is typically used to interface to high-performance stereo codecs such as

Crystal’s CS4216/18.

After the MCP is enabled, SCLK begins to transition at the programmed clock rate and the start of the

first frame is signalled by pulsing the SFRM pin high for one SCLK period. The rising edge of SFRM

coincides with the rising edge of SCLK. The SFRM pulse causes the MCP to transfer any available

audio and/or telecom data from their respective transmit FIFOs to a 64-bit serial shifter, setting the

appropriate audio/telecom valid flags as well. If the codec control register contains valid data, the

register value and address are placed within the appropriate fields in the shifter, and the read/write bit

is configured to indicate which type of register access is to be made. For any field that does not have

valid data available, the previous value transmitted is used. As long as the MCP is enabled, data

frames are continuously transferred, even if no valid data is available for transmission. The format of

data transmitted and received in subframe 0 is shown in

. Note that the UCB110 or

USB1200 data sheets use big-endian notation; little-endian notation is used in the following figure to

remain consistent with the rest of the SA-1100 specification.

Figure 11-31. MCP Frame Data Format

Both the MCP and the off-chip codec drive data on the rising edge of SCLK and latch data on its

falling edge. After SFRM is negated, subframe 0 begins and the data within the 64-bit shifter is

driven onto the TXD4 pin a bit at a time, starting with the MSB (bit<63>). As each bit of data is

shifted onto the TXD4 pin from one side of the shifter, a bit is also shifted into the opposite end of

the shifter from the RXD4 pin. After 64 SCLK cycles elapse, all data within the shifter has been

transmitted, and the shifter contains the 64-bit receive data frame. The MCP takes the data from

each field and places it in its respective receive FIFO or data register. The next 64 SCLK cycles

make up subframe 1. When subframe 1 is active, the clocks to all MCP resources that are not

needed are turned off in order to conserve power.

shows the pin timing of the MCP.

Figure 11-32. MCP Frame Pin Timing

Bit

63

48

47

46

43

42

41

34

33

32

3

1

1

6

1

5

0

TX

Audio Transmit Data

0

Address

R/W

00000000

AV

TV

Telecom Transmit Data

Control Register Write

RX

Audio Receive Data

0

Address

R/W

00000000

AV

TV

Telecom Receive Data

Control Register Read

AV – Audio Data Valid TV – Telecom Data Valid R/W – Write=1, Read=0 Address – Codec Register Address

Frame Clock

Count

1

2

...

63

64

65

66

...

127

128

1

Subframe

Subframe 0

Subframe 1

SCLK

...

...

SFRM

...

TXD4

Bit<63>

Bit<62>

...

Bit<1>

Bit<0>

...

Bit<63>

RXD4

Bit<63>

Bit<62>

...

Bit<1>

Bit<0>

...

Bit<63>