Zilog Z16C35 User Manual

Page 78

ISCC

User Manual

UM011002-0808

72

Only the CRC-CCITT polynomial may be used in SDLC mode. This is selected by setting

bit D2 in WR5 to “0”. This bit controls the selection for both the transmitter and receiver.

The initial state of the generator and checker is controlled by bit D7 of WR10. When this

bit is set to “1”, both the generator, and checker will have an initial value of all “1s” and, if

this bit is set to “0”, the initial values will be all “0s”.

The ISCC does not automatically preset the CRC generator so this must be done in soft-

ware. This is accomplished by issuing the Reset Tx CRC generator command, which is

encoded in bits D7 and D6 of WR0. For proper results, this command must be issued

while the transmitter is en-abled and idling. If CRC is to be used the transmit CRC gener-

ator must be enabled by setting bit D0 of WR5 to “1”. CRC is normally calculated on all

characters between opening and closing flags, so this bit is usually set to “1” at initializa-

tion and never changed.

Enabling the CRC generator is not sufficient to control the transmission of CRC. In the

ISCC this function is controlled by the Tx Underrun/EOM bit, which may be reset by the

processor and set by the ISCC.

When the transmitter underruns (both the transmit buffer and transmit shift register are

empty) the state of the Tx Underrun EOM bit determines the action taken by the ISCC.

If the Tx Underrun/EOM bit is set to “1” when the underrun occurs, the transmitter will

send flags.

The Reset Tx Underrun/EOM Latch command is encoded in bits D7 and D6 of WR0.

If this bit is reset to “0” when the underrun occurs, the transmitter will send either the

accumulated CRC followed by flags, or an abort followed by flags, depending on the state

of the Abort/Flag on Underrun bit in the WR10, Bit 1. A summary is shown in Table 4-10.

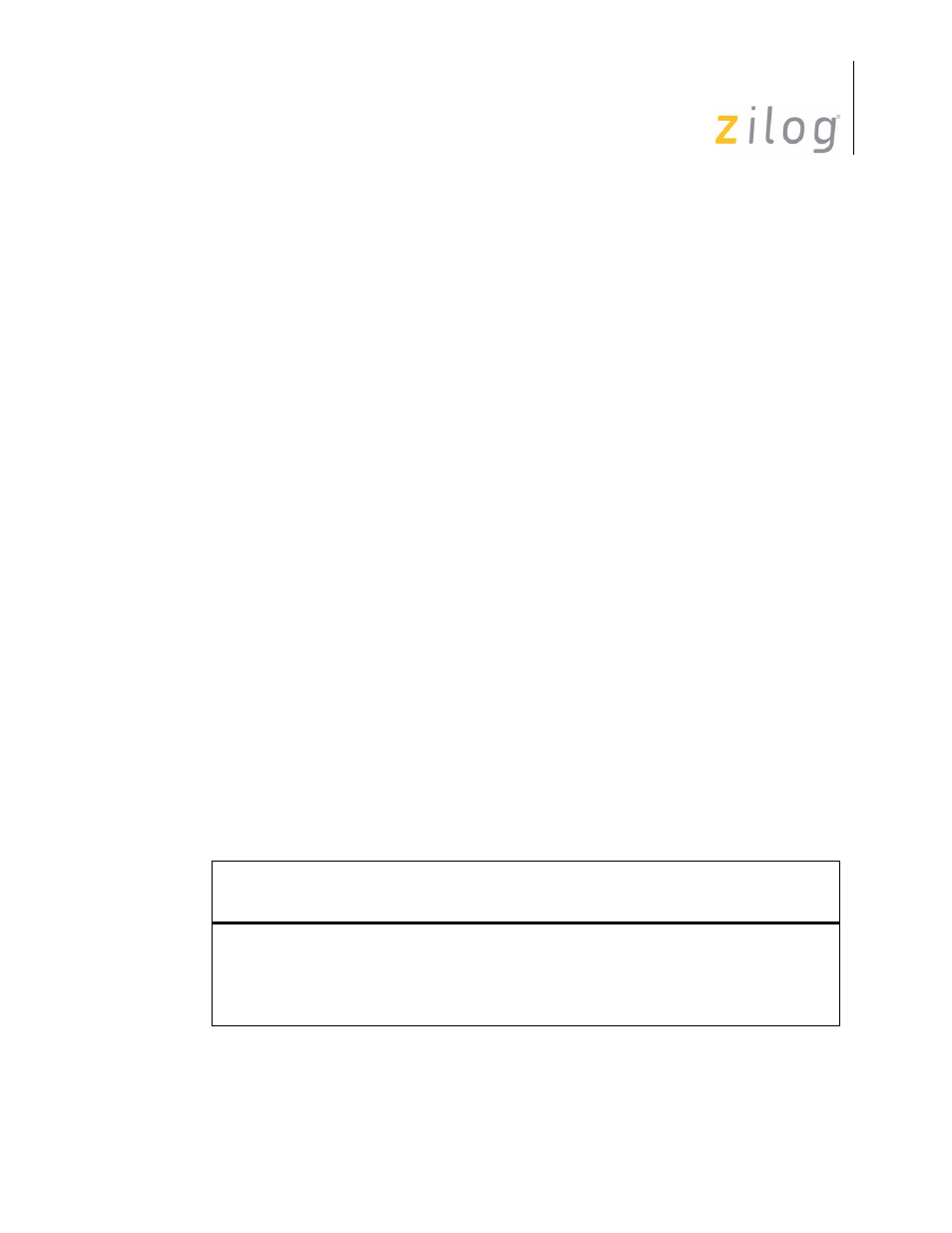

Underrun EOM Bit

The ISCC™ sets the Tx Underrun/EOM Latch when the CRC or abort is loaded into the

shift register for transmission. This event can cause an interrupt, and the status of the Tx

Table 4–18. Underrun EOM Bit

Tx Underrun /EOM Latch

Bit

Abort/Flag

Action taken by ISCC upon

Transmit Underrun

0

0

Sends CRC followed by flag

0

1

Sends abort followed by flag

1

x

Sends flag

Page 72 of 316