System interface (continued) – Zilog Z16C35 User Manual

Page 234

Application Note

SCC in Binary Synchronous Communications

10-4

SYSTEM INTERFACE

(Continued)

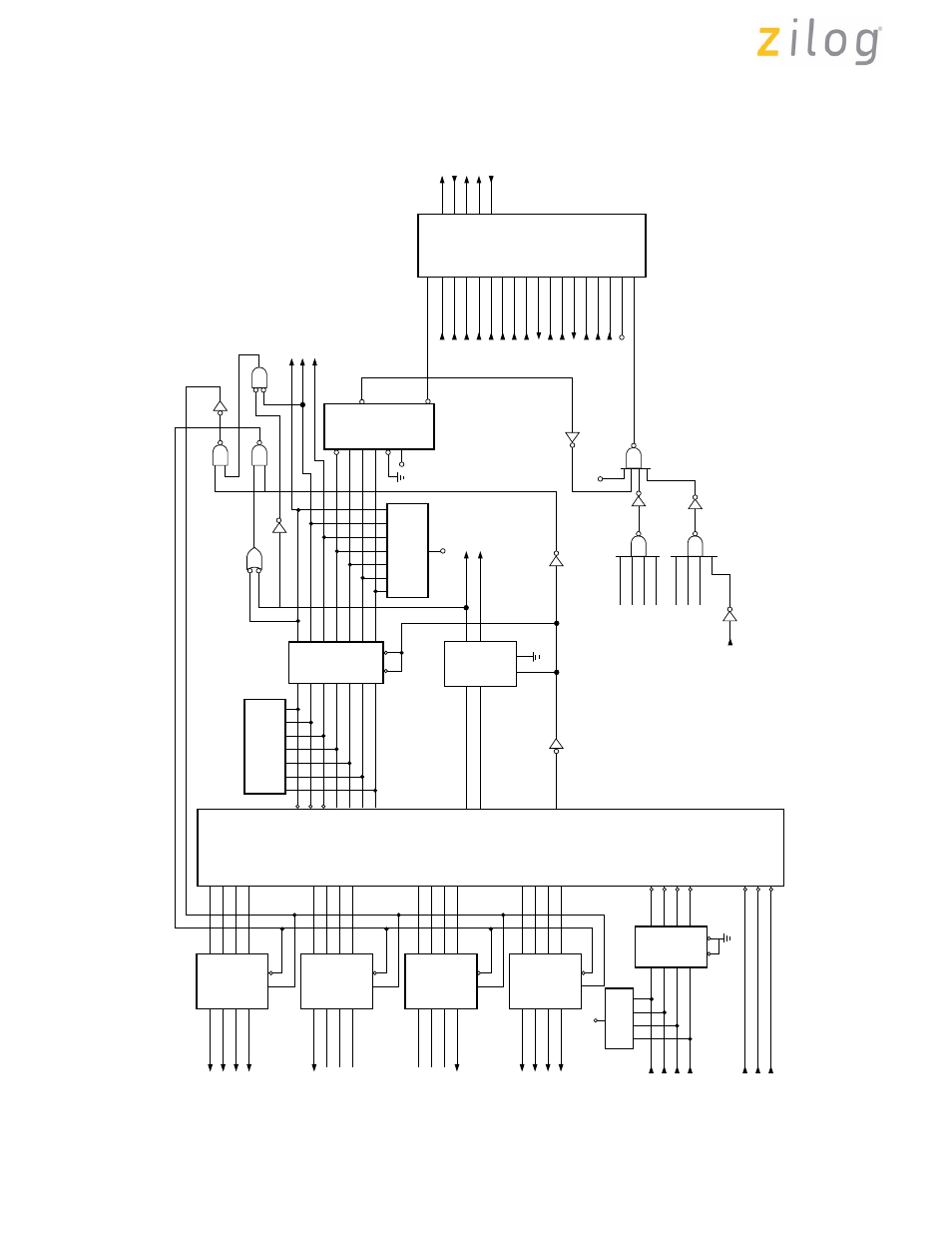

Figure 4. Z8002 with SCC

4B

3B

2B

1B

GBA

4A

3A

2A

1A

/GAB

8

9

10

11

6

5

4

3

8

9

5

4

4B

3B

2B

1B

4A

3A

2A

1A

8

9

10

11

6

5

4

3

4B

3B

2B

1B

4A

3A

2A

1A

8

9

10

11

6

5

4

3

4B

3B

2B

1B

GBA

4A

3A

2A

1A

/GAB

8

9

10

11

6

5

4

3

13 1

13 1

13 1

13 1

4.7 K

V

+5V

IAD15

IAD14

IAD13

IAD12

IAD1

1

IAD10

IAD9

IAD8

IAD7

IAD6

IAD5

IAD4

IAD3

IAD2

IAD1

IAD0

/W

AIT

/ST

OP

/VI

/NVI

/NMI

/RESET

4MHZ

AD15

AD14

AD13

AD12

3

2

1

39

AD1

1

AD10

AD9

AD8

38

37

36

35

AD7

AD6

AD5

AD4

34

33

32

40

AD3

AD2

AD1

AD0

23

6

11

12

/W

AIT

/ST

OP

/VI

/NVI

13

14

30

/NMI

/RESET

CLOCK

18

16

3

14

2

4

17

6

1 14

18

16

3

14

LS

244

/AS

/DS

/MREQ

ST3

ST2

ST1

ST0

29

17

16

18

19

20

21

2

17

4

8

13

6

15

18

3

16

12

7

14

5

5

3

2

1

4

6

LS

138

LS

243

/GAB GBA

1 13

24

25

26

3

4

11

10

IAD15

IAD14

IAD13

IAD12

IAD1

1

IAD10

IAD9

IAD8

+5V

IAD0

IAD1

IAD2

IAD3

IAD4

IAD5

IAD6

IAD7

/VI

4MHZ

+5V

/IAS

/IDS

IR//W

+5V

40

1

39

2

38

3

37

4

5

20

7

6

35

36

34

32

33

/INT

ACK

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

/INT

PCLK

IEI

IEO

/AS

/DS

R//W

CSI

/CSO

TxDA

RxDA

/TRxCA

/W

AIT

/R

TxCA

15

13

14

10

12

13 /I/O

7

+5V

+5V

IR//W

IN//S

/EN

C

B

A

/EN

EN

/Y2

/IAS

/IDS

/IMREQ

4.7 K

V

4.7 K

V

LS

244

LS

243

Z8030

/VIACK

/R//W

N//S

/BUSACK

Z8002

Page 228 of 316

UM011002-0808