Zilog Z16C35 User Manual

Page 278

Application Note

Boost Your System Performance Using The Zilog ESCC

™

13-11

1

DMA Request on Transmit Deactivation

Timing /DTR//REQ.

Timing implementation in the ESCC has been improved to

make it more compatible with the DMA cycle timing

(Reference Tech Manual, Section 2.5.2; DMA Request on

Transmit).

Transmission of Back-To-Back Frames with

a Shared Flag.

The ESCC provides facilities to allow transmission of

back-to-back frames with a shared flag between frames

(Figure 13).

In the ESCC, if the Automatic End Of Message (EOM)

Reset feature is enabled (WR7' D1=1), data for a second

frame is written to the transmit FIFO when Tx

Underrun/EOM interrupt has occurred. This allows

application software sufficient time to write the data to the

transmit FIFO while allowing the current frame to be

concluded with CRC and flag.

In the SCC, Transmission of Back-to-Back Frames is more

difficult because (Figure 14):

1.

Data cannot be written to the transmitter at EOF until

a Transmit Buffer Empty interrupt is generated after

CRC has completed transmission.

2.

Automatic EOM Reset is not available in the SCC.

Application software has to issue the “Reset

Tx/Underrun EOM” command manually. The software

overhead limits the next frame data to deliver

immediately after the preceding frame has been

concluded with CRC and Flag.

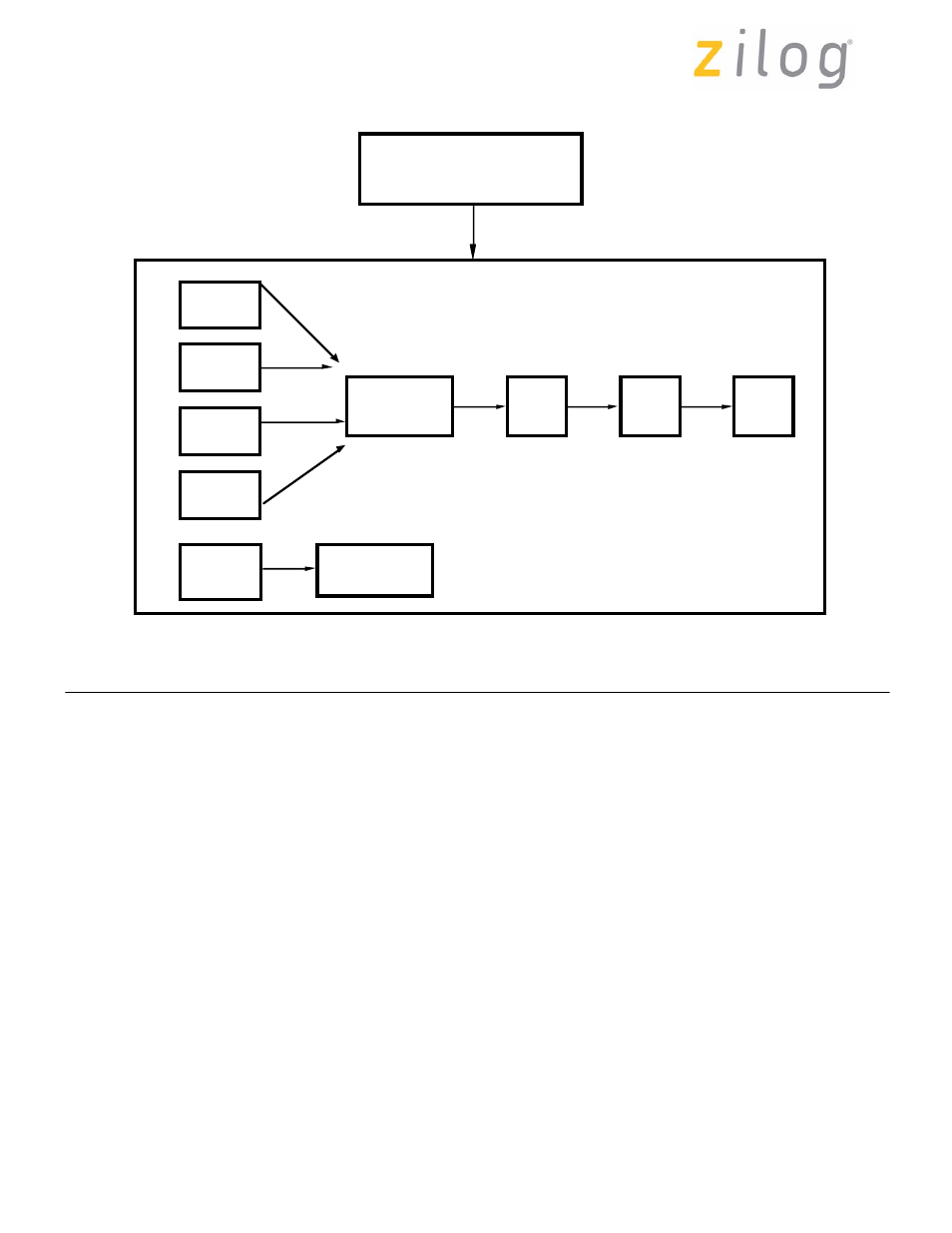

Figure 12. Receive Interrupt Mechanism 2

Receive Interrupt on 1st

Special Conditions or In

Receive Characters or Spec

Receive Char

Available In

Specia

Conditi

Interr

Data

FIFO

Locke

Erro

Rese

Data

FIFO

Unloc

CRC err

Overrr

Error

Pari

Erro

End o

Frame

Receiv

Char.

Availa

Page 272 of 316

UM011002-0808