1 dpll operation in the nrzi mode, Dpll operation in the nrzi mode – Zilog Z16C35 User Manual

Page 41

ISCC

User Manual

UM011002-0808

35

the receiver samples the data in the middle of the bit cell. In NRZI mode, the DPLL does

not require a transition in every bit cell, so this mode is useful for recovering the clocking

information from NRZ and NRZI data streams.

In the FM mode, the DPLL clock must be 16 times the data rate. In this mode the transmit

clock output of the DPLL lags the receive clock outputs by 90 degrees to make the trans-

mit and receive bit cell boundaries the same, because the receiver must sample FM data at

one-quarter and three-quarters bit time.

3.5.1 DPLL Operation in the NRZI Mode

To operate in NRZI mode, the DPLL must be supplied with a clock that is 32 times the

data rate. The DPLL uses this clock, along with the receive data, to construct receive and

transmit clock outputs that are phased to properly receive and transmit data.

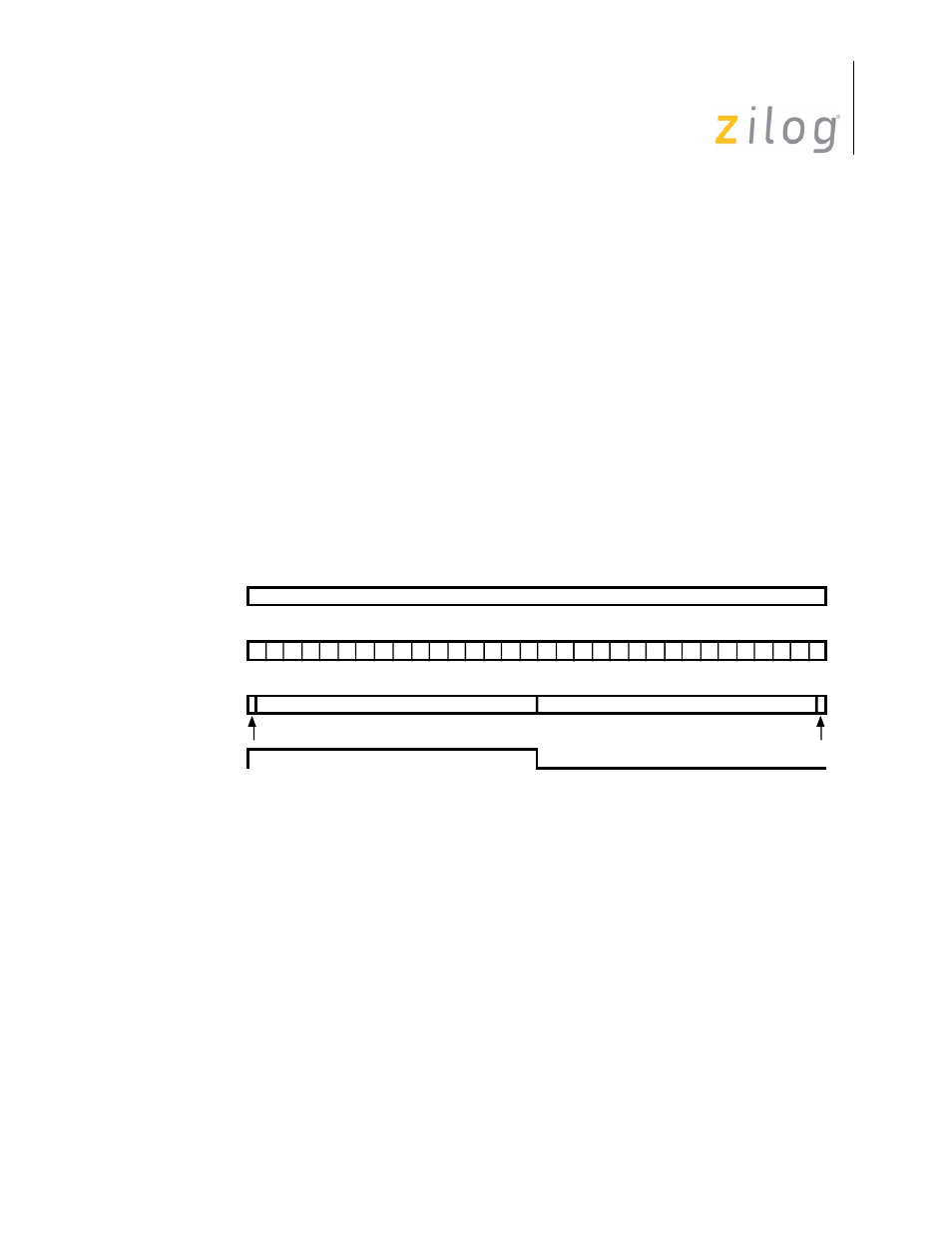

To do this, the DPLL divides each bit cell into four regions, and makes an adjustment to

the count cycle of the 5-bit counter dependent upon in which region a transition on the

receive data input occurred. This is shown in Figure 3-5.

Figure 3–8. DPLL in NRZI Mode

Ordinarily, a bit cell boundary will occur between count 15 and count 16, and the DPLL

output will cause the data to be sampled in the middle of the bit cell. However, four differ-

ent situations may happen:

The DPLL actually allows the transition marking a bit cell boundary to occur anywhere

during the second half of count 15 or the first half of count 16 without making a correction

to its count cycle.

If the transition marking a bit cell boundary occurs between the middle of count 16 and

count 31, the DPLL is sampling the data too early in the bit cell. In response to this, the

DPLL extends its count by one during the next 0 to 31 counting cycle, which effectively

moves the edge of the clock that samples the receive data closer to the center of the bit

cell.

1

18 19 20

17

16

21 22 23 24 25 26 27 28 29 30 31

2 3 4 5

7 8 9

12 13 14

11

10

15

0

No Change

No Change

Bit Cell

Count

Connection

DPLL Out

Add One Count

Subtract One Count

6

Page 35 of 316