Zilog Z16C35 User Manual

Page 71

ISCC

User Manual

UM011002-0808

65

5. At the end of eight-bit-times F is in the 8-bit delay and G is in the Receive Shift regis-

ter. At this time G is transferred to the receive data FIFO. Character G must be read

and discarded by the processor. Eight bit times later H is transferred to the receive data

FIFO also. The result of a CRC calculation is latched in the receive error FIFO at the

same time as data is written to the receive data FIFO. Thus the CRC result through

character F accompanies character H in the FIFO and will be valid in RR1 until char-

acter H is read from the receive data FIFO. The CRC checker may be disabled and

reset at any time after character H is transferred to the receive data FIFO. Recall, how-

ever, that internally CRC will not be disabled until after this occurs. A better alterna-

tive is to place the receiver in Hunt mode, which automatically disables and resets the

CRC checker. See Table 4-8 for a condensed description.

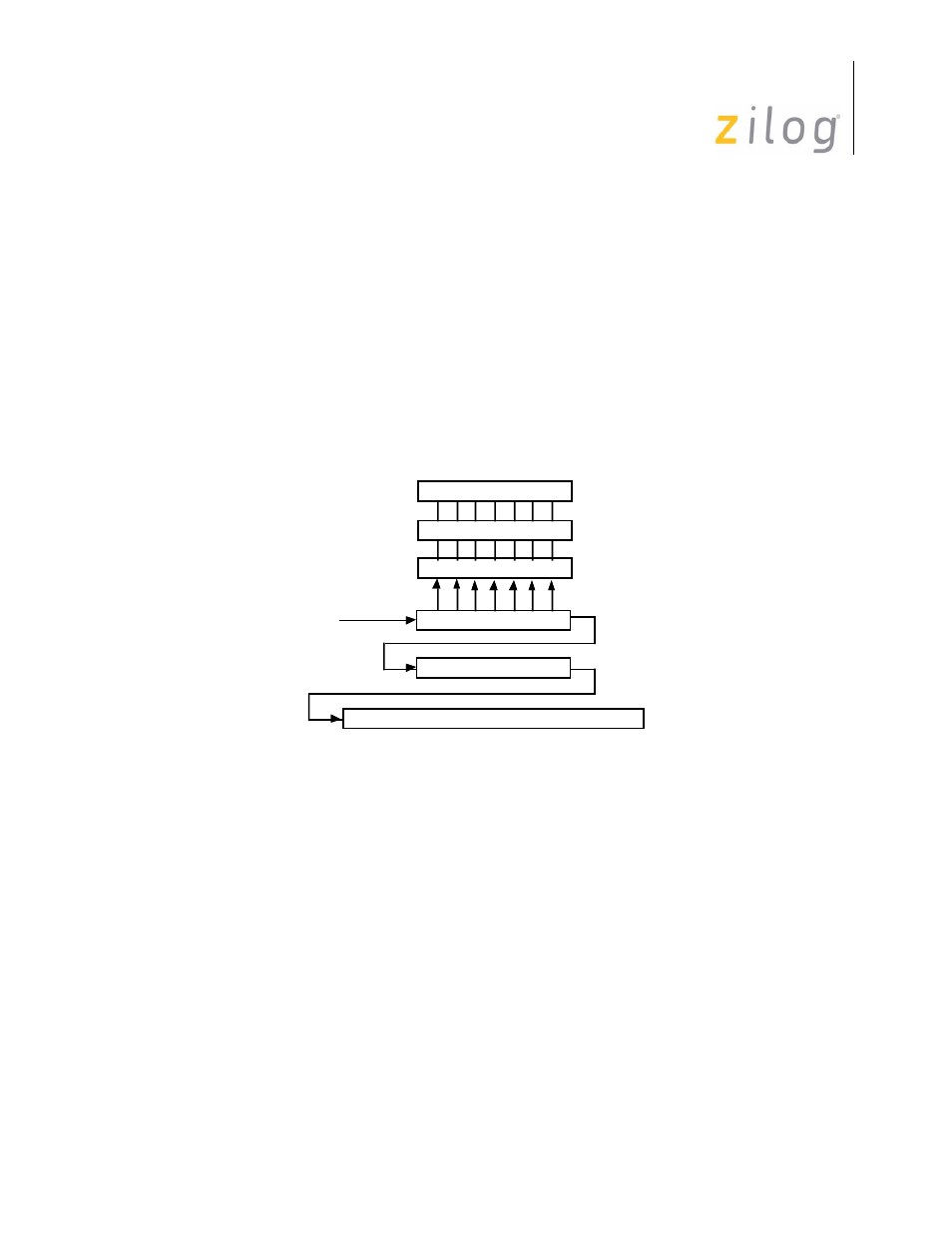

Figure 4–24. Receive CRC Data Path

Receive Data FIFO

Receive Shift Register

CRC Checker

Eight Bit Time Delay

Receive Data

Page 65 of 316