7 dma enable register, Dma enable register – Zilog Z16C35 User Manual

Page 143

ISCC

User Manual

UM011002-0808

137

Bit 6 reflects the Transmit A DMA Interrupt Under Service status. The function of this bit

is identical to that for bit 7.

Bit 5 reflects the Receive B DMA Interrupt Under Service status. The function of this bit

is identical to that for bit 7.

Bit 4 reflects the Transmit B DMA Interrupt Under Service status. The function of this bit

is identical to that for bit 7.

Bit 3 reflects the Receive A DMA Interrupt Pending (IP) status. This bit can be set or

cleared through a command (see Interrupt Command Register). This bit will be set to 1

automatically when a Receive A DMA interrupt condition occurs. An interrupt will be

requested if the corresponding Interrupt Enable bit is set to 1, if the DMA Master Interrupt

Enable bit is set to 1, and if the ISCC IEI input is 1, and if the corresponding IUS bit is 0.

Bit 2 reflects the Transmit A DMA Interrupt Pending status. The function of this bit is

identical to that for bit 3.

Bit 1 reflects the Receive B DMA Interrupt Pending status. The function of this bit is iden-

tical to that for bit 3.

Bit 0 reflects the Transmit B DMA Interrupt Pending status. The function of this bit is

identical to that for bit 3.

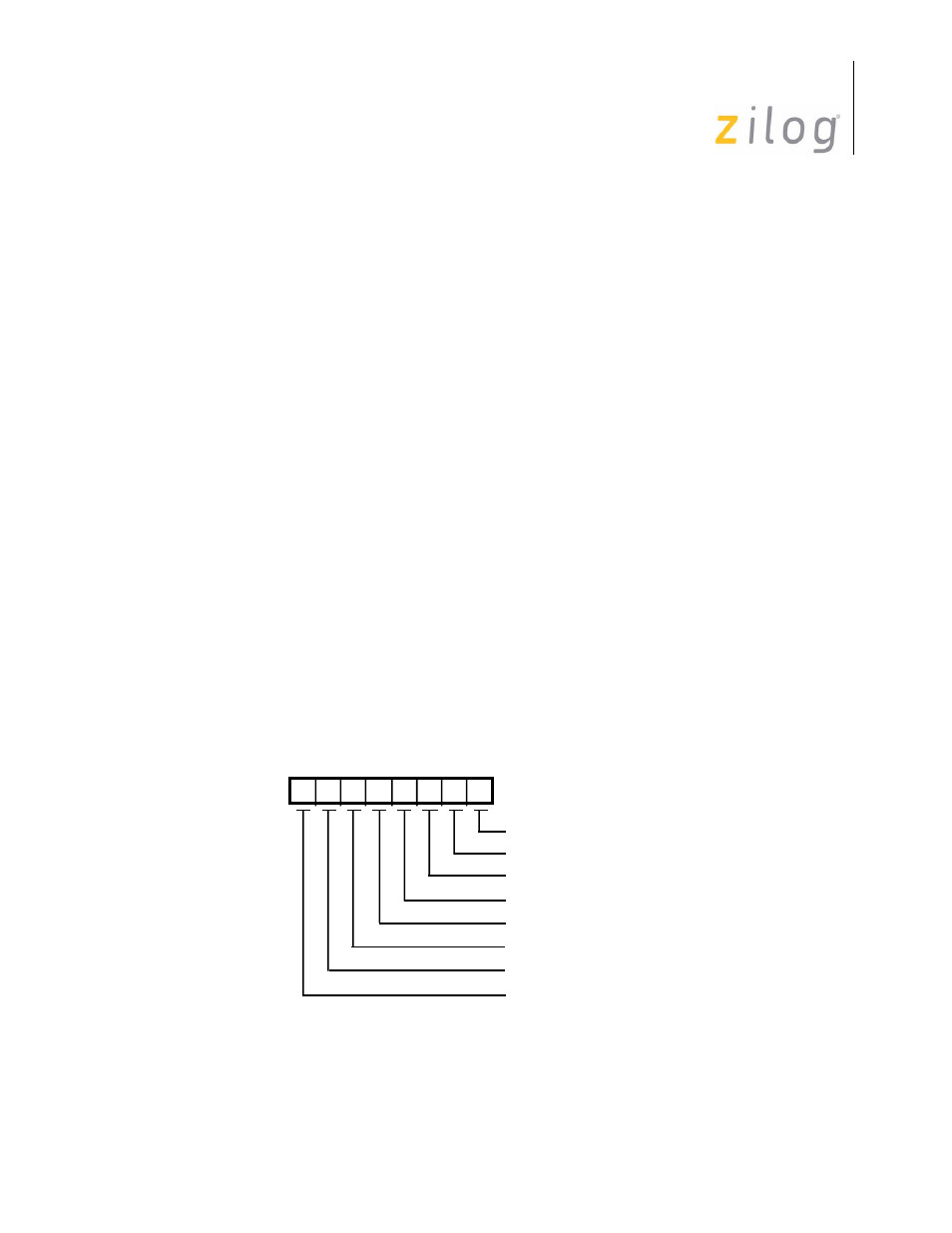

5.6.7 DMA Enable Register

This register controls the enabling of the DMA channels and contains the enables for the

DMA Abort Interrupt conditions. The bit positions for this register are shown in Figure

5-32.

Figure 5–61. DMA Enable Register

Address: 00100

D6

D7

D5 D4 D3 D2 D1 D0

Tx B DMA Abort Enable

Rx B DMA Abort Enable

Tx A DMA Abort Enable

Rx A DMA Abort Enable

Tx B DMA Enable

Rx B DMA Enable

Tx A DMA Enable

Rx A DMA Enable

Page 137 of 316