4 read register 3, Read register 3 – Zilog Z16C35 User Manual

Page 132

ISCC

User Manual

UM011002-0808

126

Figure 5–49. Read Register 2

5.5.4 Read Register 3

RR3 is the interrupt Pending register. The status of each of the interrupt Pending bits in the

SCC cell is reported in this register. This register exists only in Channel A. If this register

is accessed in Channel B, all “0’s” are returned. The two unused bits are always returned

as “0”. Figure 5-21 shows the bit positions for RR3.

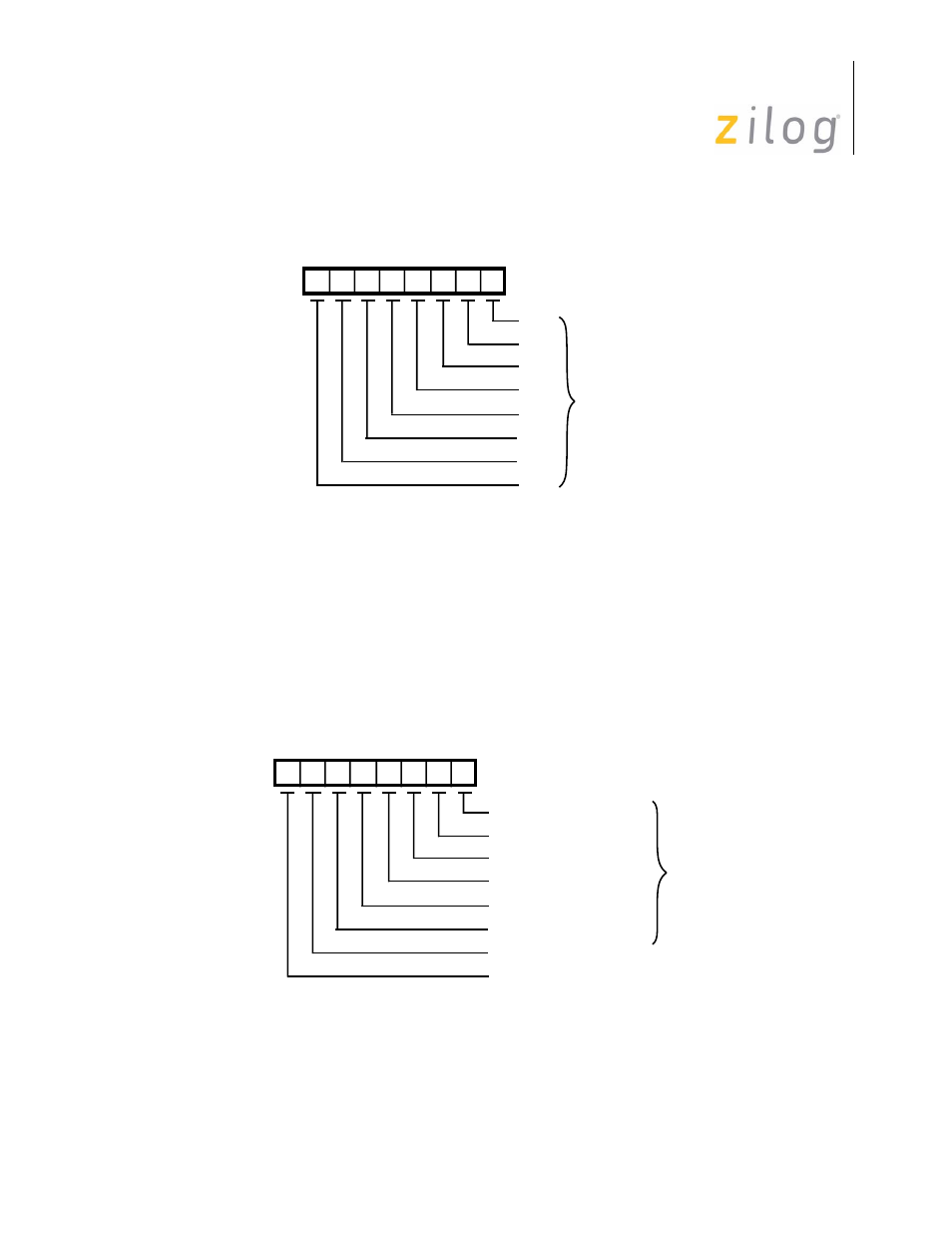

Figure 5–50. Read Register 3

Read Register 2

D6

D7

D5 D4 D3 D2 D1 D0

V0

V1

V2

V3

V4

V5

V6

V7

* Modified in B Channel

Interrupt

Vector *

Read Register 3

D6

D7

D5 D4 D3 D2 D1 D0

Channel B Ext/Status IP

Channel B Tx IP

Channel B Rx IP

Channel A Ext/Status IP

Channel A Tx IP

Channel A Rx IP

0

0

* Always 0 in B Channel

*

Page 126 of 316

See also other documents in the category Zilog Sensors:

- S3F94C8 (11 pages)

- S3F80QB (29 pages)

- S3F8S19 (38 pages)

- Z51F6412 (96 pages)

- Z51F6412 (54 pages)

- Z51F6412 (55 pages)

- EZ80F93 (11 pages)

- Z16F6411 (20 pages)

- Z16F6411 (216 pages)

- EZ80F93 (13 pages)

- ZMOT0BSB (314 pages)

- ZMOT0BSB (582 pages)

- Z8F083A (14 pages)

- Z8F2480 (17 pages)

- Z8F082A (18 pages)

- Z8F082A (15 pages)

- Z8F6423 (83 pages)

- Z8F0822 (17 pages)

- Z8F2480 (19 pages)

- Z8F2480 (18 pages)

- Z8F6423 (18 pages)

- Z8F6423 (27 pages)

- Z8F6482 (50 pages)

- EZ80F915 (411 pages)

- EZ80F91NAA (34 pages)

- EZ80F91 (41 pages)

- EZ80L92 (40 pages)

- EZ80L92 (26 pages)

- EZ80L92 (79 pages)

- EZ80F91GA (469 pages)

- EZ80L92 (10 pages)

- eZ80F92 (87 pages)

- Z16FMC6 (520 pages)

- Z8FMC16 (26 pages)

- Z16FMC6 (41 pages)

- ZUSBOPTS (38 pages)

- ZUSBOPTS (59 pages)

- Z16FMC6 (26 pages)

- Z16FMC6 (8 pages)

- ZMOT1AHH (25 pages)

- ZMOT0BSB (34 pages)

- EZ80F915 (78 pages)

- EZ80190 (87 pages)

- EZ80L92 (86 pages)

- EZ80F91GA (127 pages)