Zilog Z16C35 User Manual

Page 57

ISCC

User Manual

UM011002-0808

51

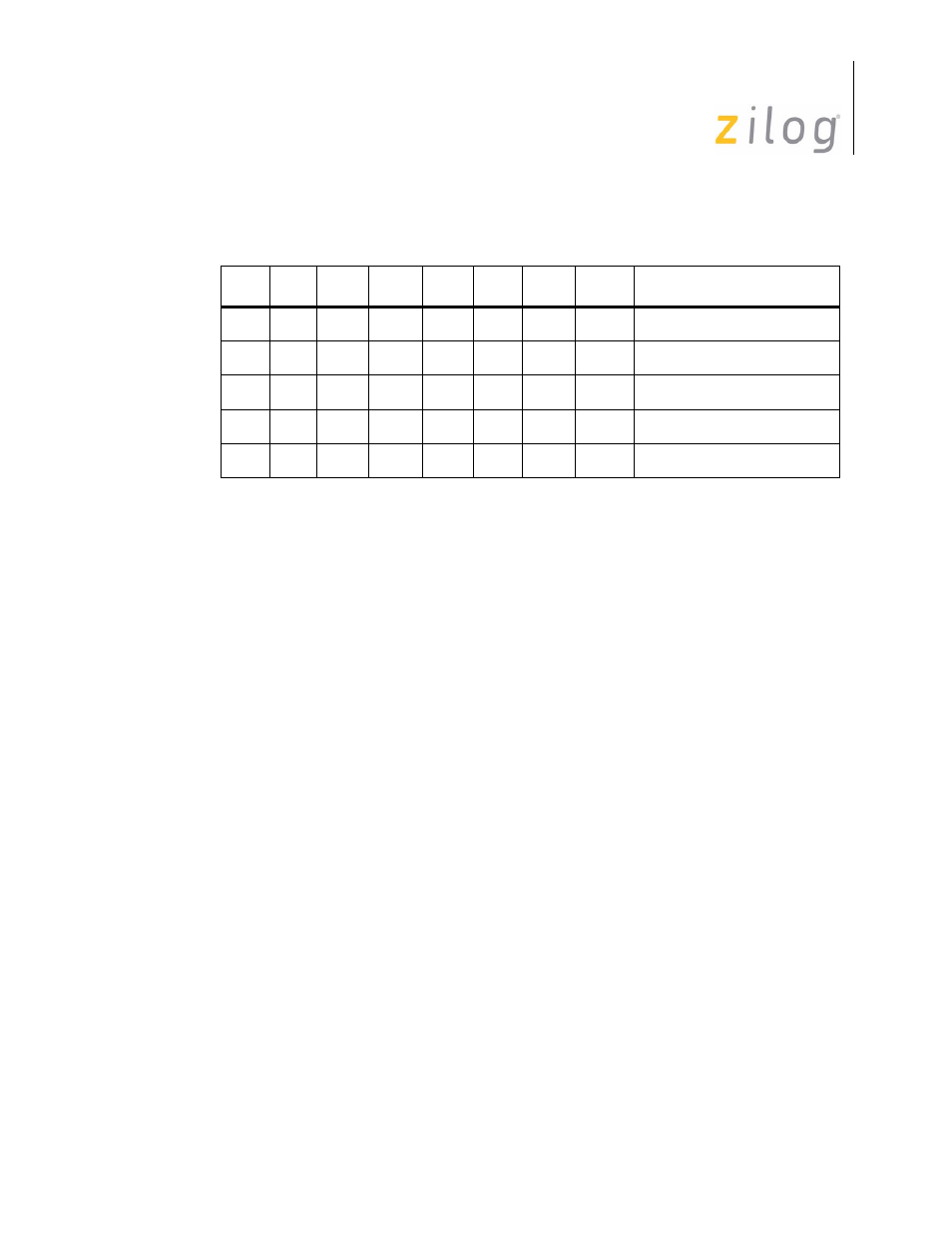

For five or less bits per character selection in WR5, the following encoding is used in the

data sent to the transmitter. D is the data bit(s) to be sent.

In all cases the data must be right-justified, with the unused bits being ignored except in

the case of five bits or less per character.

An additional bit, carrying parity information, may be automatically appended to every

transmitted character by setting bit D0 of WR4 to “1”. This bit is sent in addition to the

number of bits specified in WR4 or by the data format. The parity sense is selected by bit

D1 of WR4. If this bit is set to “1”, the transmitter sends even parity, if set to “0”, the par-

ity is odd.

The ISCC may be programmed to accept a transmit clock that is one, sixteen, thirty-two,

or sixty-four times the data rate. This is selected by bits D7 and D6 of WR4, in common

with the clock factor for the receiver. Note that the chosen clock factor may restrict the

number of stop bits that may be transmitted. In particular, when the clock rate and data

rate are identical, one-and-a-half stop bits are not allowed. If any length other than one

stop bit is desired in the times one mode, only two stop bits may be used.

There are two modem control signals associated with the transmitter provided by the

ISCC, namely /RTS and /CTS.

The /RTS pin is a simple output that carries the inverted state of the RTS bit (D1) in WR5,

unless the Auto Enables bit (D5) is set in WR3. When Auto Enables is set, the /RTS pin

will immediately go Low when the RTS bit is set. However, when the RTS bit is reset, the

/RTS pin remains Low until the transmitter is completely empty and the last stop bit has

left the TxD pin. Thus the /RTS pin may be used to disable external drivers for the trans-

mit data.

The /CTS pin is ordinarily a simple input to the CTS bit in RR0. However, if Auto Enables

mode is selected this pin becomes an enable for the transmitter. That is, if Auto Enables is

on and the /CTS pin is High, the transmitter is disabled; the transmitter is enabled while

the /CTS pin is Low.

The transmitter may be programmed to send a Break by setting bit D4 of WR5 to “1”. The

transmitter will send continuous “0s” from the first transmit clock edge after this com-

D7

D6

D5

D4

D3

D2

D1

D0

1

1

1

1

0

0

0

D

Sends one data bit

1

1

1

0

0

0

D

D

Sends two data bits

1

1

0

0

0

D

D

D

Sends three data bits

1

0

0

0

D

D

D

D

Sends four data bits

0

0

0

D

D

D

D

D

Sends five data bits

Page 51 of 316