2 dpll operation in the fm modes, Dpll operation in the fm modes – Zilog Z16C35 User Manual

Page 42

ISCC

User Manual

UM011002-0808

36

If the transition occurs between count 0 and the middle of count 15, the output of the

DPLL is sampling the data too late in the bit cell. To correct this, the DPLL shortens its

count by one during the next 0 to 31 counting cycle, which effectively moves the edge of

the clock that samples the receive data closer to the center of the bit cell.

If the DPLL does not see any transition during a counting cycle, no adjustment is made in

the following counting cycle.

If an adjustment to the counting cycle is necessary, the DPLL modifies count 5, either

deleting it or doubling it. Thus, only the LOW time of the DPLL output will be lengthened

or shortened.

While the DPLL is in search mode, the counter remains at count 16 where the DPLL out-

puts are both HIGH. The missing clock latches in the DPLL which may be accessed in

RR10. They are not used in NRZI mode. An example of the DPLL in operation is shown

in Figure 3-6.

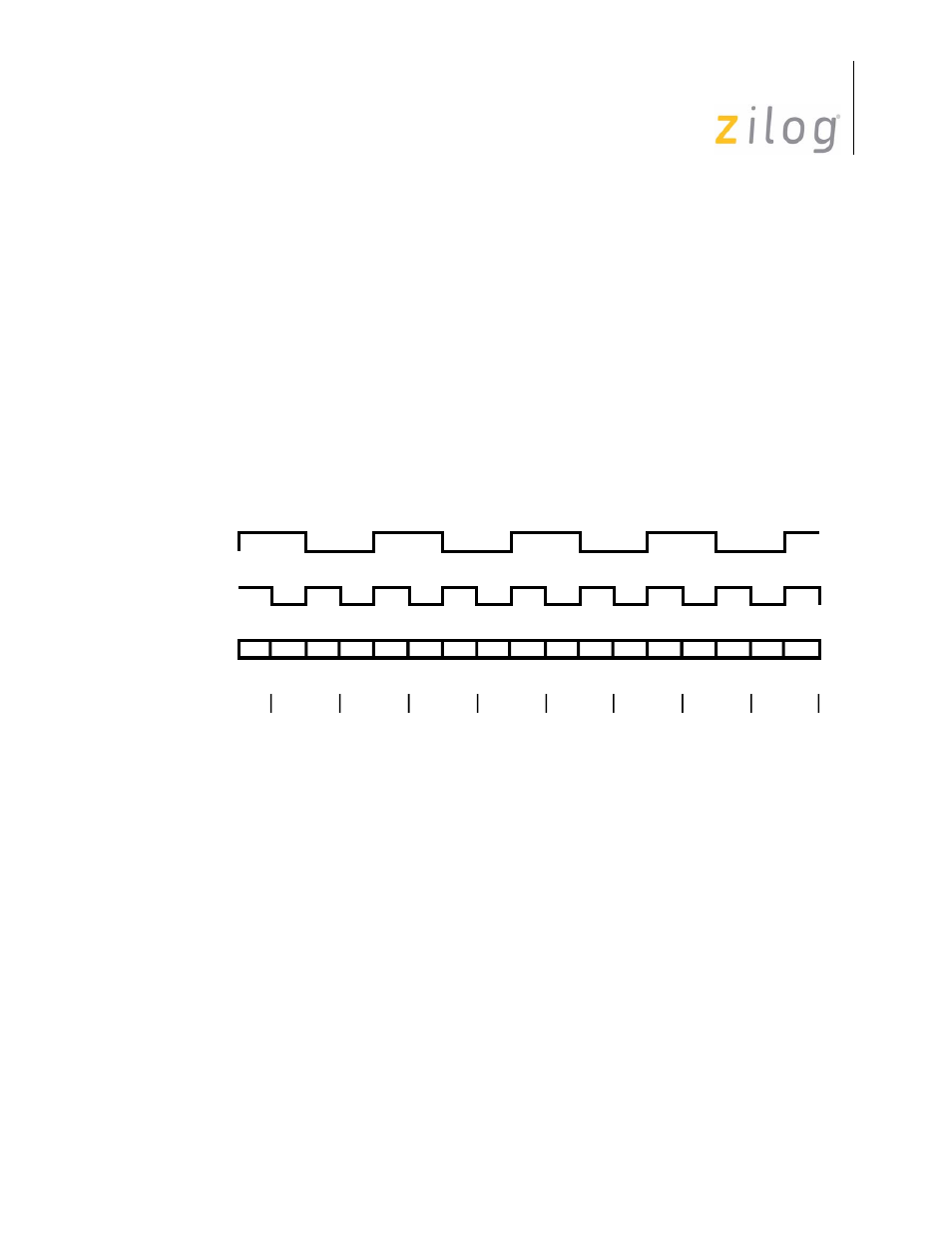

Figure 3–9. DPLL Operating Example (NRZI Mode)

3.5.2 DPLL Operation in the FM Modes

To operate in FM mode, the DPLL must be supplied with a clock that is 16 times the data

rate. The DPLL uses this clock, along with the receive data, to construct receive and trans-

mit clock outputs that are phased to receive and transmit data properly.

In FM mode one cycle of the counter in the DPLL is a count from 0 to 31, but now each

cycle corresponds to 2-bit cells. To make adjustments to remain in phase with the receive

data, the DPLL divides a pair of bit cells into 5 regions, making the adjustment to the

Receive

Data

DPLL

Output

Correction

Windows

Count

Length

32 32 32 31 31 31 33 33 33

+1 -1 +1 -1 +1 -1 +1 -1 +1 -1 +1 -1 +1 -1 +1 -1 +1

Page 36 of 316