2 external reset -18, 3 internal system reset -18, Figure 2-9. maxq7665/maxq7666 external reset -18 – Maxim Integrated MAXQ7666 User Manual

Page 90: 2 external reset, 3 internal system reset

2.7.2 External Reset

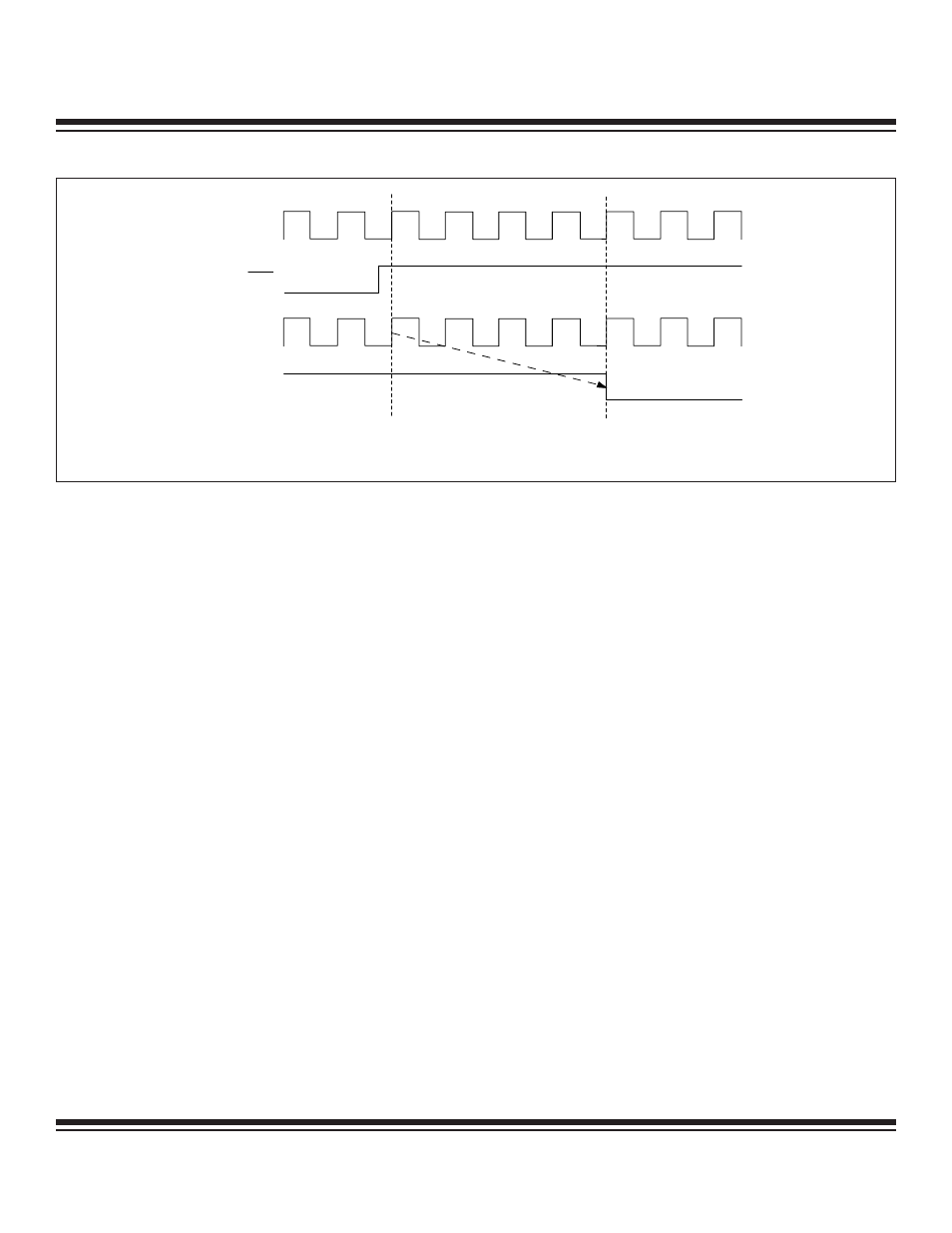

During normal operation, the MAXQ7665/MAXQ7666 devices are placed into an external reset mode by holding the

RESET pin low for

at least four clock cycles. If the MAXQ7665/MAXQ7666 devices are in the low-power stop mode (i.e., system clock is not active), the

RESET pin becomes an asynchronous source, forcing the reset state immediately after being taken to logic 0. Once the MAXQ7665/

MAXQ7666 enter reset mode, it remains in reset as long as the

RESET pin is held at logic 0. After the RESET pin returns to logic 1, the

processor starts the internal 7.6MHz RC oscillator if necessary and exits the reset state within four clock cycles (Figure 2-9) and begins

program execution at address 8000h.

The

RESET pin is an output and an input. If a reset condition is caused by an internal source (such as a brownout reset, watchdog, or

internal reset), an output reset pulse or low level is generated at the

RESET pin as long as the MAXQ7665/MAXQ7666 remain in reset.

If the

RESET pin is connected to an incompatible external reset circuit, it may not be able to drive the output reset signal. However, if

this occurs it does not affect the internal reset condition.

Because the XT bit in the CKCN register and the HFE bit in the OSCC register are cleared to 0 only on power-on reset, it is possible to

exit an external reset with the clock source set to the high-frequency crystal oscillator. In this case, execution resumes running from

the RC oscillator, and the switchover to the high-frequency oscillator occurs automatically when the crystal oscillator is ready.

2.7.3 Internal System Reset

The MAXQ7665/MAXQ7666 support internal system reset capability from in-system programming mode. An internal system reset is

generated when the ROD bit in the system control register is set. The SPE bit in the ICDF register must also be set. The bootloader

software can use this capability to initiate an internal system reset when the flash loader completes its operation. See

Section 12 for

more details on in-system programming.

MAXQ7665/MAXQ7666 User’s Guide

2-18

Figure 2-9. MAXQ7665/MAXQ7666 External Reset

SYSTEM CLOCK

RESET

RESET

SAMPLING

INTERNAL

RESET

FIRST

INSTRUCTION

FETCH

Maxim Integrated