3 true-differential analog input t/h -20, Table 3-3. pga gain and channel input capacitance, 3 true-differential analog input t/h – Maxim Integrated MAXQ7666 User Manual

Page 110

MAXQ7665/MAXQ7666 User’s Guide

3-20

3.3.3 True-Differential Analog Input T/H

The equivalent input circuit of Figure 3-4 A and B shows the MAXQ7665/MAXQ7666’s analog input architecture when the PGA is

bypassed (PGA disabled and PGA gain = 1). In track mode, a positive input capacitor is connected to AIN0, AIN2, AIN4…AIN14 and

a negative input capacitor is connected to AIN1, AIN3, AIN5…AIN15 in differential mode. T/H timing is controlled by the ADC source

select (ADCS2:ADCS0) and ADC dual-mode select (ADCUL) fields in the ADC control register (ACNT). ADCS selects an ADC con-

version start source, which could be one of the timers, ADCCNV pin, or software writes to the ADC start bit. All three conversion start

sources support single-edge or dual-edge modes of operation, which are determined by the ADCDUL bit. When ADCDUL is set to 1,

the ADC operates in dual-edge mode. The rising edge of the selected conversion start source causes the ADC to power up and begin

acquisition; the falling edge causes it to sample and perform a conversion. If ADCDUL is set as 1, make sure the PGA gain (selected

by the PGG2:PGG0 bits in the APE register) is greater than 1. Setting ADCDUL = 1 and PGA gain = 1 is illegal. When ADCDUL is 0,

the ADC operates in single-edge mode. The rising edge controls the entire conversion, i.e., power-up, acquisition, and conversion

sequence if the ADC was off; if the ADC was on, it stays in acquisition mode until the rising edge and then starts conversion. Once a

conversion has been initiated, the T/H enters acquisition mode for the next conversion on the 13th falling edge of ADCCLK, if auto shut-

down (ADCASD = 0 in ADC control register) is disabled. See

Section 3.3.10 for ADC conversion start sources and timing details.

The time required for the T/H to acquire an input signal is determined by how quickly its input capacitance is charged. If the input sig-

nal’s source impedance is high, the acquisition time lengthens. The acquisition time, t

ACQ

, is the minimum time needed for the signal

to be acquired. It is calculated by the following equation:

t

ACQ

≥ k x (R

SOURCE

+ R

IN

) x C

IN

Where:

k = 9

≈ ln (2 x 2

12

)

The constant, k, is the number of RC time constants required so that the voltage on the internal sampling capacitor reaches 12-bit

accuracy, i.e., so that the difference between the input voltage and the sampling capacitor voltage is equal to 0.5 LSB.

R

SOURCE

is the source impedance of the input signal, R

IN

= 1k

Ω is the equivalent differential analog input resistance, and C

IN

= 14pF

is the equivalent differential analog input capacitance when PGA = 1. Note that for PGA = 1, t

ACQ

is never less than 375ns (3 ADCCLK

periods at 8MHz), and any source impedance less than 1k

Ω does not significantly affect the ADC’s AC performance. For higher source

impedance, a longer acquisition time is required.

For PGA > 1, t

ACQ

requires an additional 5µs (40 ADCCLK cycles at 8MHz). The additional cycles are due to PGA settling time and

automatically introduced by the internal hardware. The PGA uses a switched capacitor technique (see

Section 3.3.6), and channel

input capacitance C

IN

increases with gain as shown in Table 3-3.

With PGA > 1, any source impedance less than 5k

Ω does not significantly affect the ADC’s AC performance.

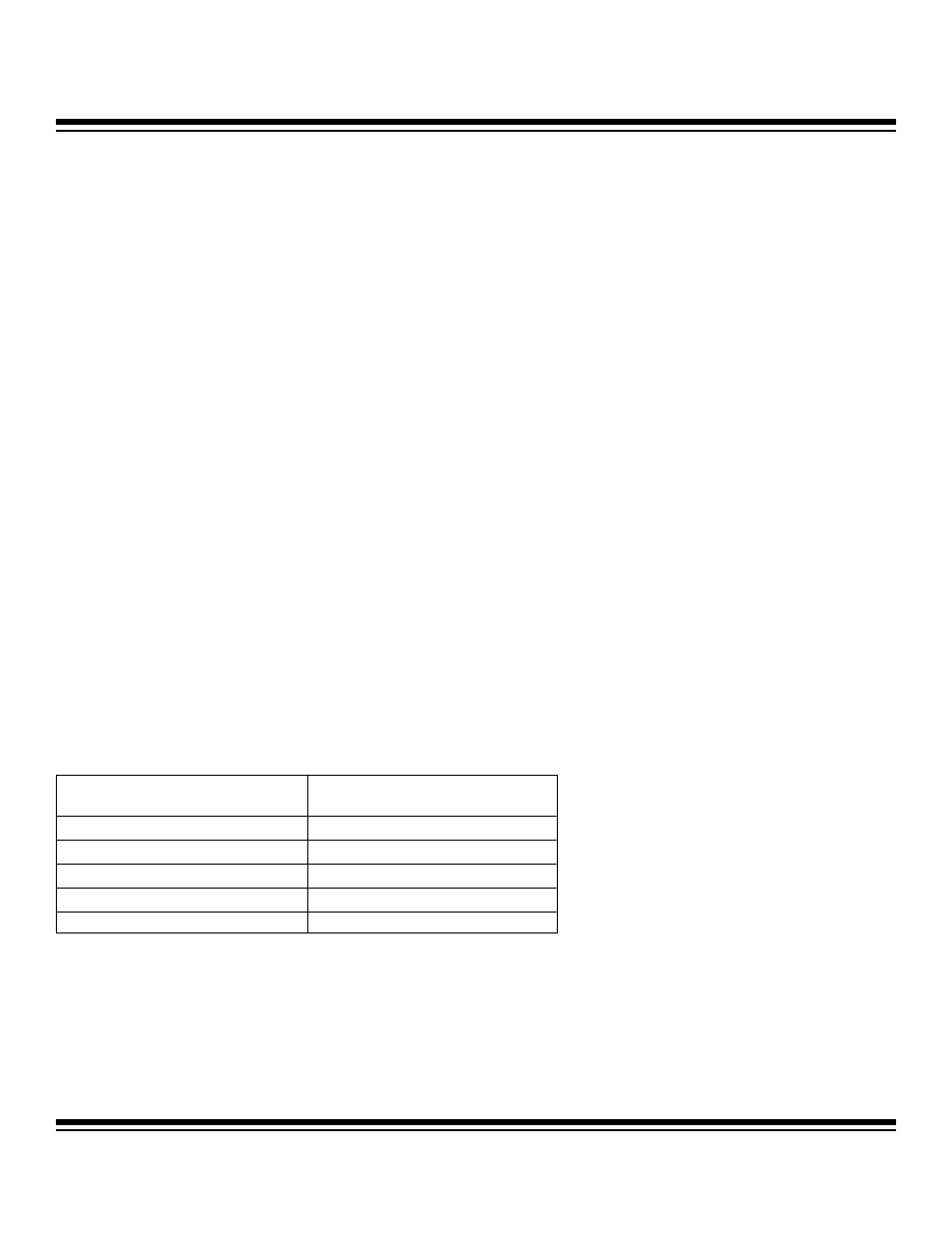

Table 3-3. PGA Gain and Channel Input Capacitance

PGA

C

I N

(pF)

(C

I N

= C

I N +

= C

I N -

)

x2 2

x4 4

x8 8

x16 16

x32 32

Maxim Integrated