1 tap overview -3, 2 architecture -3, 1 tap overview – Maxim Integrated MAXQ7666 User Manual

Page 289: 2 architecture

SECTION 10: TEST ACCESS PORT (TAP)

10.1 TAP Overview

The MAXQ7665/MAXQ7666 incorporate a test access port (TAP) and TAP controller for communication with a host device across a

4-wire synchronous serial interface. The MAXQ7665/MAXQ7666 use the TAP to support in-system flash programming, in-circuit debug,

and device test functions. The MAXQ7665/MAXQ7666 TAP features include the following:

• 4-wire synchronous communication

• TAP signals compatible with JTAG IEEE Standard 1149.1

• Maximum TAP clock frequency limited to 1/8 the system clock

For detailed information on the TAP and TAP controller, refer to IEEE STD 1149.1

"IEEE Standard Test Access Port and Boundary-Scan

Architecture." Except where explicitly noted, the MAXQ7665 and MAXQ7666 features are identical.

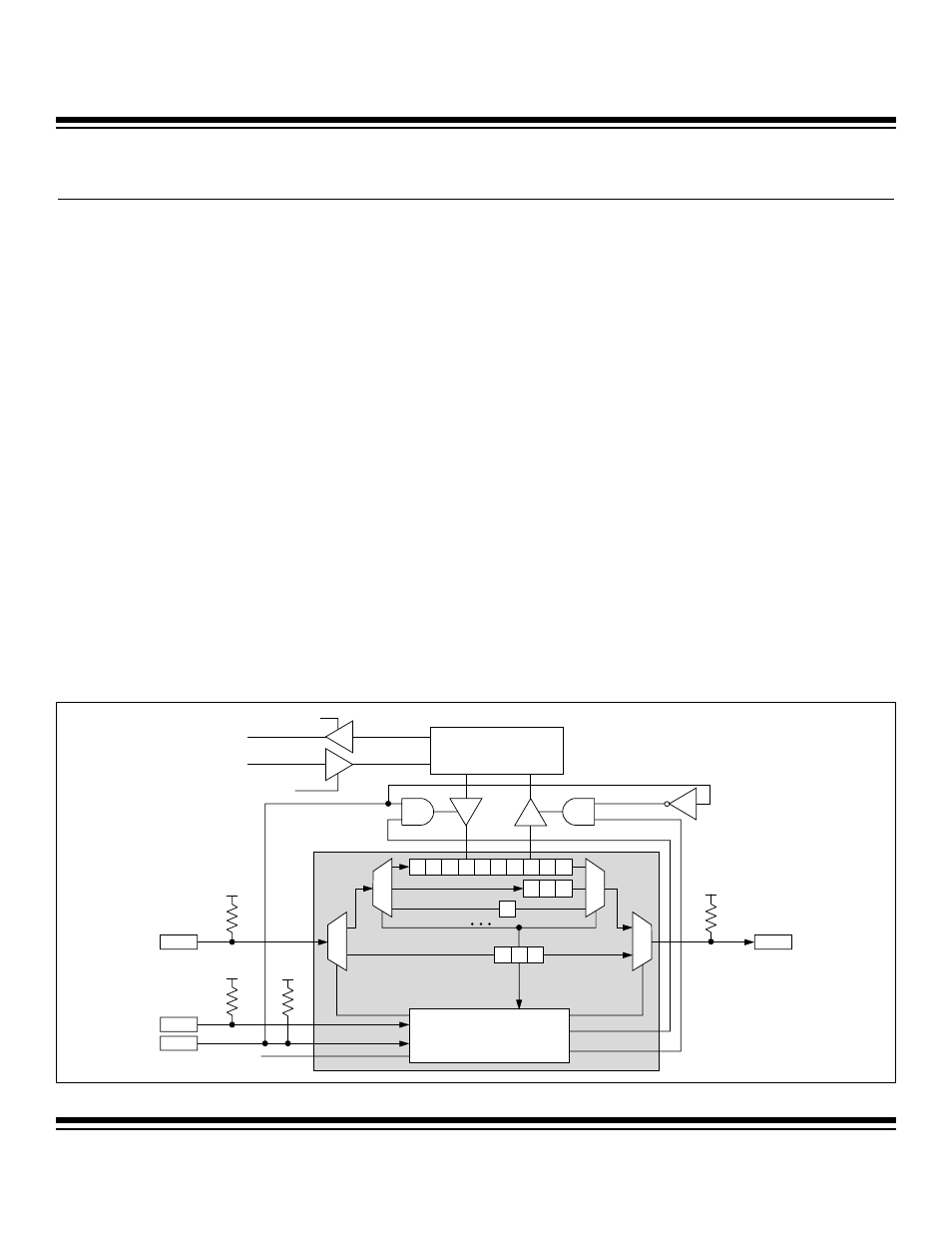

10.2 Architecture

The MAXQ7665/MAXQ7666 TAP controller is a synchronous state machine that responds to changes at the TMS and TCK signals. The

TAP state control is achieved through host manipulation of the test mode select (TMS) and test clock (TCK) signals. Based on its state

transition, the controller provides the clock and control sequence for TAP operation. The performance of the TAP is dependent on the

TCK clock frequency. The maximum TCK clock frequency should be limited to 1/8 the system clock frequency. Figure 10-1 shows a

simplified functional block diagram of the MAXQ7665/MAXQ7666 TAP and TAP controller.

The TAP provides an independent serial channel to communicate synchronously with the host system. The TMS signal is sampled at

the rising edge of TCK and decoded by the TAP Controller to control movement between the TAP states. The TDI input and TDO out-

put are meaningful once the TAP is in a serial shift state.

The TAP controller block has four working registers that control the operation of the port.

• TAP Debug Register

• TAP System Programming Register

• TAP Instruction Register

• TAP Bypass Register

These registers are accessed through the TAP port only and control the sequencing of the TAP state machine. These registers are not

accessible from the CPU.

MAXQ7665/MAXQ7666 User’s Guide

10-3

Figure 10-1. MAXQ7665/MAXQ7666 TAP and TAP Controller

P0.0/TDO

DVDDIO

DVDDIO

DVDDIO

P0.2/TDI

WRITE

P0.3/TCK

DEBUG REGISTER

UPDATE-DR

UPDATE-DR

P0.1/TMS

SYSTEM PROGRAMMING

REGISTER

READ

TO DEBUG

ENGINE

SHADOW

REGISTER

POWER-ON

RESET

BYPASS

INSTRUCTION REGISTER

7

6

5

4

3

2

1

0

s1 s0

2

1

0

2

1

0

DVDDIO

TAP CONTROLLER

Maxim Integrated