Table 14-3. destination specifier codes -14, Table 14-3. destination specifier codes – Maxim Integrated MAXQ7666 User Manual

Page 351

MAXQ7665/MAXQ7666 User’s Guide

14-14

MOVE dst,

src

Move Data

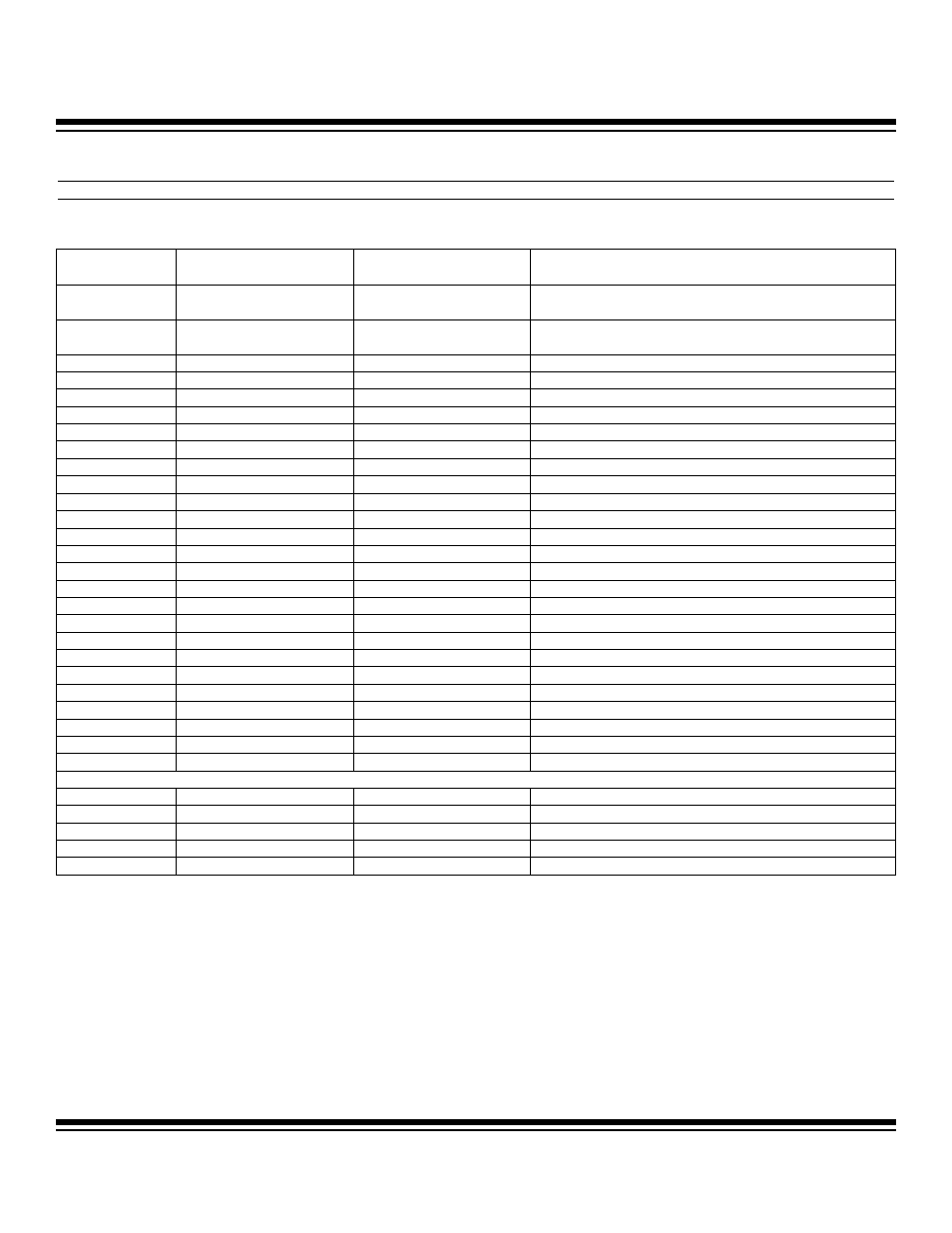

Table 14-3. Destination Specifier Codes

Data Transfer

dst (16-bit)

← src (16-bit):

dst[15:0]

← src[15:0]

Rules

dst (8-bit)

← src (8-bit):

dst[7:0]

← src[7:0]

dst (16-bit)

← src (8-bit):

dst[15:8]

← 00h *

dst[7:0]

← src[7:0]

dst (8-bit)

← src (16-bit):

dst[7:0]

← src[7:0]

*

Note: The PFX[0] register may be used to supply a separate high-order data byte for this type of transfer.

dst

dst BIT ENCODING

(ddd dddd)

WIDTH

(16 OR 8)

DESCRIPTION

NUL 111

0110

8/16

Null (Virtual) Destination. Intended as a bit bucket to assist

software with pointer increments/decrements.

MN[n] nnn

0NNN 8/16

nnnn Selects One of First 8 Registers in Module NNN; where

NNN= 0 to 5. Access to Next 24 Using PFX[n].

AP 000

1000

8

Accumulator

Pointer

APC

001 1000

8

Accumulator Pointer Control

PSF

100 1000

8

Processor Status Flag Register

IC

101 1000

8

Interrupt and Control Register

IMR

110 1000

8

Interrupt Mask Register

A[n]

nnn 1001

8/16

nnn Selects 1 of First 8 Accumulators: A[0]..A[7]

Acc

000 1010

8/16

Active Accumulator = A[AP]

PFX[n]

nnn 1011

8

nnn Selects One of 8 Prefix Registers

@++SP

000 1101

16

16-Bit Word @SP, Pre-Increment SP

SP 001

1101

16

Stack

Pointer

IV 010

1101

16

Interrupt

Vector

LC[n]

11n 1101

16

n Selects 1 of 2 Loop Counter Registers

@BP[OFFS]

000 1110

8/16

Data Memory @BP[OFFS]

@BP[++OFFS]

001 1110

8/16

Data Memory @BP[OFFS]; Pre-Increment OFFS

@BP[--OFFS]

010 1110

8/16

Data Memory @BP[OFFS]; Pre-Decrement OFFS

OFFS

011 1110

8

Frame Pointer Offset from Base Pointer (BP)

DPC

100 1110

16

Data Pointer Control Register

GR 101

1110

16

General

Register

GRL

110 1110

8

Low Byte of GR Register

BP

111 1110

16

Frame Pointer Base Pointer (BP)

@DP[n]

n00 1111

8/16

Data Memory @DP[n]

@++DP[n]

n01 1111

8/16

Data Memory @DP[n], Pre-Increment DP[n]

@--DP[n]

n10 1111

8/16

Data Memory @DP[n], Pre-Decrement DP[n]

DP[n]

n11 1111

16

n Selects 1 of 2 Data Pointers

2

-CYCLE DESTINATION ACCESS USING PFX[n] REGISTER (See Special Notes)

SC 000

1000

8

System

Control

Register

CKCN

110 1000

8

Clock Control Register

WDCN

111 1000

8

Watchdog Control Register

A[n]

nnn 1001

16

nnn Selects 1 of Second 8 Accumulators A[8]..A[15]

GRH

001 1110

8

High Byte of GR Register

Maxim Integrated