21 frame pointer base register (bp) -58, 22 general register byte-swapped (grs) -58, 21 frame pointer base register (bp) – Maxim Integrated MAXQ7666 User Manual

Page 60: 22 general register byte-swapped (grs)

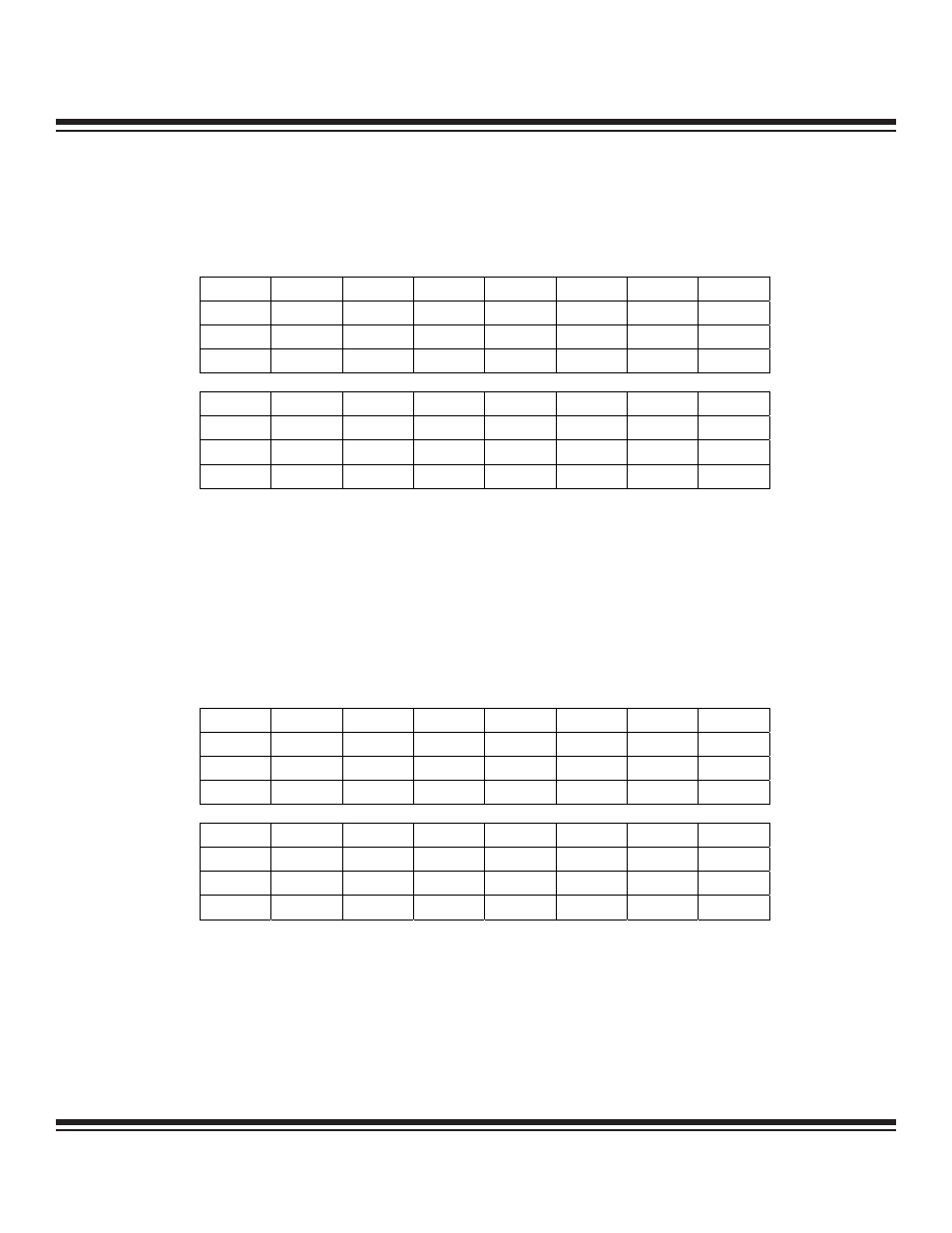

1.4.21 Frame Pointer Base Register (BP)

Register Description:

Frame Pointer Base Register

Register Name:

BP

Register Address:

Module 0Eh, Index 07h

Bits 15 to 0: Frame Pointer Base Register Bits 15 to 0 (BP.15 to BP.0). This register serves as the base pointer for the Frame Pointer

(FP). The Frame Pointer is formed by unsigned addition of Frame Pointer Base Register (BP) and Frame Pointer Offset Register (OFFS).

The content of this base pointer register is not affected by increment/decrement operations performed on the offset (OFFS) register.

1.4.22 General Register Byte-Swapped (GRS)

Register Description:

General Register Byte-Swapped

Register Name:

GRS

Register Address:

Module 0Eh, Index 08h

Bits 15 to 0: General Register Byte-Swapped Bits 15 to 0 (GRS.15 to GRS.0). This register is intended primarily for supporting byte

operations on 16-bit data. This 16-bit read-only register returns the byte-swapped value for the data contained in the GR register.

MAXQ7665/MAXQ7666 User’s Guide

1-58

Bit #

15

14

13

12

11

10

9

8

Name

BP.15 BP.14 BP.13 BP.12 BP.11 BP.10 BP.9 BP.8

Reset

0 0 0 0 0 0 0 0

Access rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

BP.7 BP.6 BP.5 BP.4 BP.3 BP.2 BP.1 BP.0

Reset

0 0 0 0 0 0 0 0

Access rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Note: This register is cleared to 0000h on all forms of reset.

Bit #

15

14

13

12

11

10

9

8

Name

GRS.15 GRS.14 GRS.13 GRS.12 GRS.11 GRS.10 GRS.9 GRS.8

Reset

0 0 0 0 0 0 0 0

Access r

r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name

GRS.7 GRS.6 GRS.5 GRS.4 GRS.3 GRS.2 GRS.1 GRS.0

Reset

0 0 0 0 0 0 0 0

Access r

r

r

r

r

r

r

r

r = read

Note: This register is cleared to 0000h on all forms of reset.

Maxim Integrated