1 can 0 control register (c0c) -22 – Maxim Integrated MAXQ7666 User Manual

Page 152

MAXQ7665/MAXQ7666 User’s Guide

4-22

4.2.4 CAN Global Control and Status Register Descriptions

All the global CAN controls and status, as well as the individual message center control/status registers, are located in the peripheral

register map. These registers are located in Module 4, indexes 0h–9h, 11h–1Fh.

Note: All the registers located in the peripheral register map are directly accessible by the microcontroller using the module/index

address.

4.2.4.1 CAN 0 Control Register (C0C)

Register Description:

CAN 0 Control Register

Register Name:

C0C

Register Address:

Module 04h, Index 00h

Bits 15 to 8: Reserved. Read 0, write ignored.

Bit 7: CAN 0 Error Interrupt Enable (ERIE). Programming the ERIE bit to 1 enables the CAN 0 status bus status (BSS) or error count

greater than 96 bit (EC96) to issue an interrupt to the microcontroller, if the C0IE bit in the COR peripheral register is also set. When

ERIE is cleared to 0, the error interrupt is disabled.

Bit 6: CAN 0 Status Interrupt Enable (STIE). Programming the STIE bit to 1 allows the CAN 0 status error bits (ER0:ER2), transmit

status bit (TXS), receive status bit (RXS), or the wake-up status bit (WKS) to issue an interrupt to the microcontroller if the C0IE bit in

the COR peripheral register is also set. When STIE is cleared to 0, the status interrupt is disabled.

Bit 5: CAN 0 Power-Down Enable (PDE). Programming the PDE bit to 1 places the CAN 0 controller into a fully static power-down mode

after completion of the last reception, transmission, or after the arbitration was lost or an error condition occurred. Note that the term

"after arbitration lost" denotes the fact that the arbitration was lost and the reception following this lost arbitration is completed. Recall

that the CAN processor immediately becomes a receiver after it has lost its arbitration on the CAN bus. Programming PDE = 0 disables

the power-down mode. The PDE mode forces all the CAN 0 logic to a static state. The PDE mode can only be removed by either soft-

ware reprogramming the PDE bit or through a system reset. A read of PDE establishes when the power-down mode has been enabled

or removed as per the PDE bit. In all cases, the CAN controller begins operation after 11 recessive bits (a power-up sequence) on the

CAN bus per the configuration settings for bit timing, which were programmed prior to entering the power-down mode. Since WKS

reflects when the CAN has entered the low-power state as per the SIESTA and/or PDE bit states, a read of the PDE bit establishes when

the PDE bit is actually allowed to enable the low-power state. If the low-power state was previously enabled by setting the SIESTA bit, a

read of PDE reflects the actual PDE bit value and not the low-power mode. If the low-power mode has not been previously enabled and

the PDE bit is set to 1 by software, a read of PDE returns a 0, until such time the PDE bit actually enables the low-power mode following

an active transmit or receive operation. When the PDE and SIESTA bit are not used together, a read of the PDE bit, by default, also reflects

the actual state of the low-power mode. Setting PDE does not alter any CAN block controls or error status relationships.

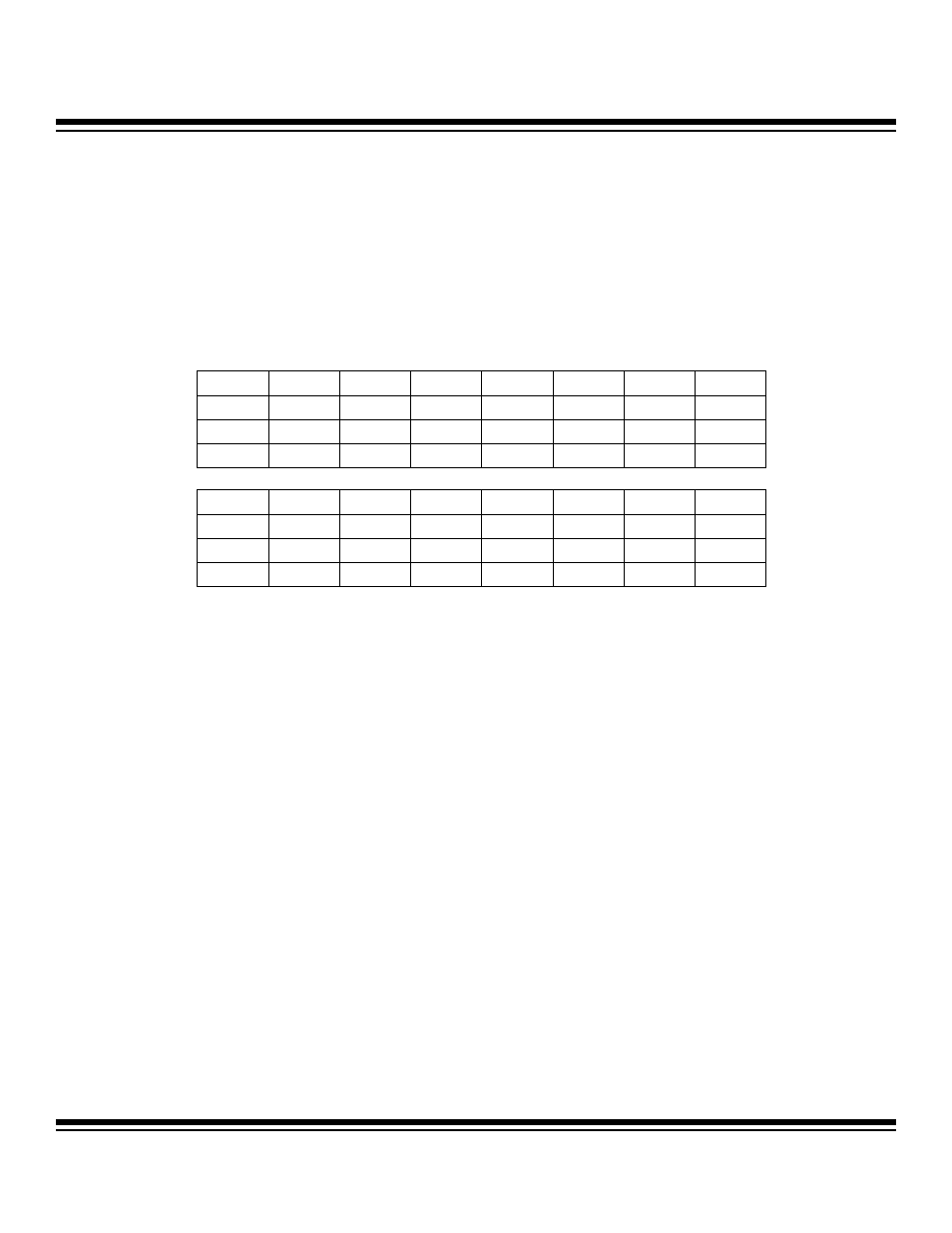

Bit #

15

14

13

12

11

10

9

8

Name

— — — — — — — —

Reset

0 0 0 0 0 0 0 0

Access

r

r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name ERIE

STIE

PDE

SIESTA

CRST

AUTOB

ERCS

SWINT

Reset

0 0 0 0 1 0 0 1

Access rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Maxim Integrated