4 measure duty cycle repeatedly -25 – Maxim Integrated MAXQ7666 User Manual

Page 260

MAXQ7665/MAXQ7666 User’s Guide

7-25

7.4.4 Measure Duty Cycle Repeatedly

To measure the duty cycle of the signal seen on the T0 input pin, the Type 2 timer is configured for a single-shot delayed run with both

edges defined for capture. The CPRL2 bits should be configured to 1 to request reloads on each edge. To prevent reloads on one of

the edges, gating should be enabled. The T2POL0 bit specifies which edge starts/ends the capture cycle and which edge does not

have a reload associated with it.

; ------------------ Reset State: T2R0 = T2V0 = T2C0 = 0000h ------------------------

MOVE T2CFG0, #00000110b

;

; T2DIV[2:0]

=000

(/1)

; T2MD

=0

(16-bit)

; CCF[1:0]

=11

(both edges)

; C/T2

=0

(timer/capture)

MOVE T2CNA0, #10101111b

; ET2

=1

(enable Timer ints)

; T2OE0

=0

(input)

; T2POL0

=1

(no reload on rising edge

;

single shot start/end on falling edge)

; TR2L:TR2

=01

(start timer on single shot condition)

; CPRL2

=1

(reload on capture edge)

; SS2

=1

(single shot mode)

; G2EN

=1

(gating enabled)

; ------------------ TCC2 Interrupt : LOW TIME=T2C0

;------------------- TCC2 Interrupt : PERIOD = T2C0

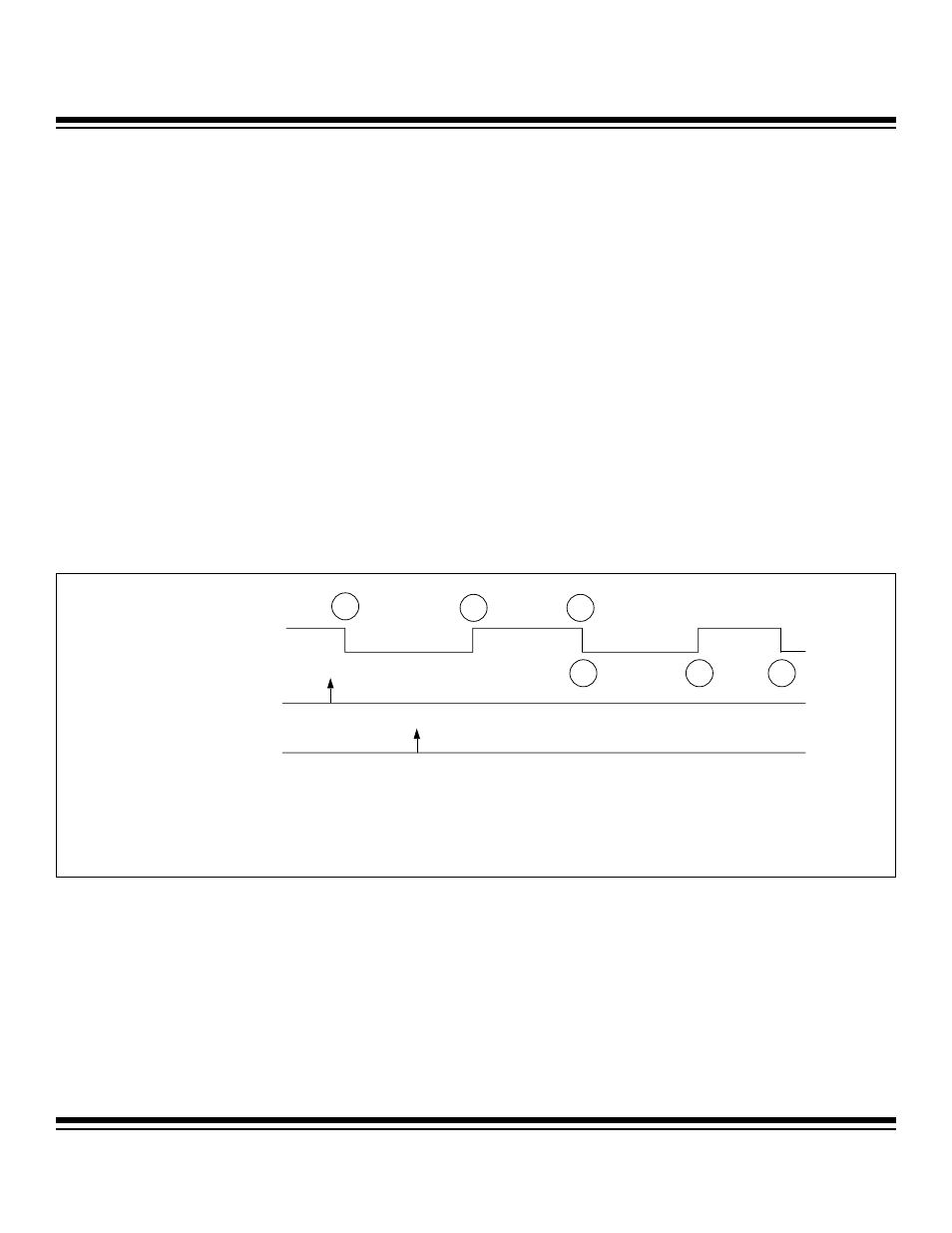

T0 PIN

CODE EXECUTION:

POINT A

CODE EXECUTION:

POINT B

1A

3A

1B

3B

2A

2B

EVENTS:

1A: FALLING EDGE CAUSES CAPTURE/RELOAD; SINGLE-SHOT CAPTURE CYCLE BEGINS.

2A: RISING EDGE CAUSES CAPTURE; LOW TIME = T2C0.

3A: FALLING EDGE CAUSES CAPTURE/RELOAD; SINGLE-SHOT CAPTURE CYCLE ENDS; PERIOD = T2C0. TIMER CONTINUES TO OPERATE

SINCE TR2 = 1, ALLOWING THE NEXT LOW TIME/PERIOD TO BE MEASURED.

1B–3B: SAME SEQUENCE AS 1A–3A, EXCEPT THAT THE SINGLE-SHOT CAPTURE CYCLE DOES NOT BEGIN UNTIL THE FIRST FALLING EDGE IS DETECTED.

Figure 7-9. Type 2 Timer Application Example—Measure Duty Cycle

Maxim Integrated