2 oscillator/clock generation registers -5, 1 analog status register (asr) -5, 2 oscillator/clock generation registers – Maxim Integrated MAXQ7666 User Manual

Page 202: 1 analog status register (asr)

5-5

MAXQ7665/MAXQ7666 User’s Guide

5.2 Oscillator/Clock Generation Registers

The MAXQ7665/MAXQ7666 oscillator/clock generation module registers are described here. All these registers are directly accessible

by the microcontroller through the module/index address.

5.2.1 Analog Status Register (ASR)

The ASR register contains the high-frequency oscillator ready and failure flags. This register is cleared to its default state when it is

read.

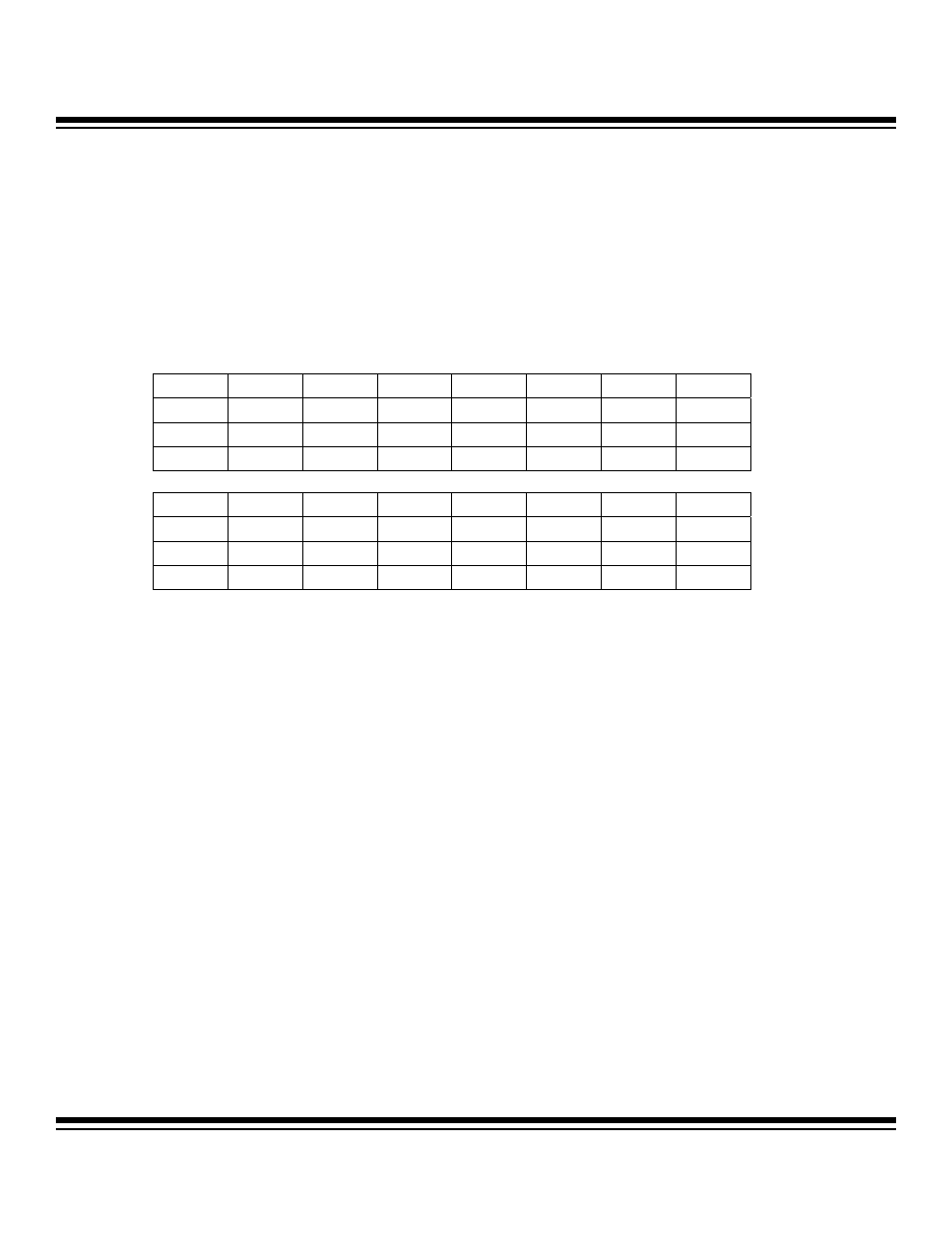

Register Description:

Analog Status Register

Register Name:

ASR

Register Address:

Module 05h, Index 0Bh

Bit 15: I/O Voltage Brownout Comparator Level (VIOLVL). See

Section 2 for more information on this bit.

Bit 14: Digital Voltage Brownout Comparator Level (DVLVL). See

Section 2 for more information on this bit.

Bits 13, 12, 10 to 7, 3, and 0: Reserved. Read 0, write ignored.

Bit 11: High-Frequency Oscillator Ready (XHFRY). This flag is set to logic 1 when the high-frequency crystal oscillator warmup is

complete and ready for use. This bit is cleared after reading from the ASR register.

Bit 6: External High-Frequency Oscillator Failure Flag (HFFINT). This flag is set to logic 1 if the previously stable high-frequency

clock source (XHFRY = 1) is sourced as the system clock (XT = 1) and a failure is detected (XHFRY = 0). This condition causes a hard-

ware clock switchover by forcing the internal 7.6MHz RC oscillator enable (RCE = 1) and selecting it as the system clock (XT =0).

Bit 5: I/O Voltage Brownout Flag (VIOBI). See

Section 2 for more information on this bit.

Bit 4: Digital Brownout Flag (DVBI). See

Section 2 for more information on this bit.

Bit 2: ADC Overrun Flag (ADCOV). See

Section 3 for more information on this bit.

Bit 1: ADC Data Ready Flag (ADCRY). See

Section 3 for more information on this bit.

Bit #

15

14

13

12

11

10

9

8

Name

VIOLVL

DVLVL

— —

XHFRY

— — —

Reset 0 0 0 0 0 0 0 0

Access r r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name —

HFFINT

VIOBI

DVBI

—

ADCOV*

ADCRY

—

Reset 0 0 0 0 0 0 0 0

Access r r

r

r

r

r

r

r

r = read

Note: Reading the ASR resets to 0 all the status flag bits except VIOLVL and DVLVL.

*The ADCOV bit is cleared by all forms of reset. All other bits are reset only by POR.

Maxim Integrated