12 instruction pointer register (ip) -53, 13 stack pointer register (sp) -53, 12 instruction pointer register (ip) – Maxim Integrated MAXQ7666 User Manual

Page 55: 13 stack pointer register (sp)

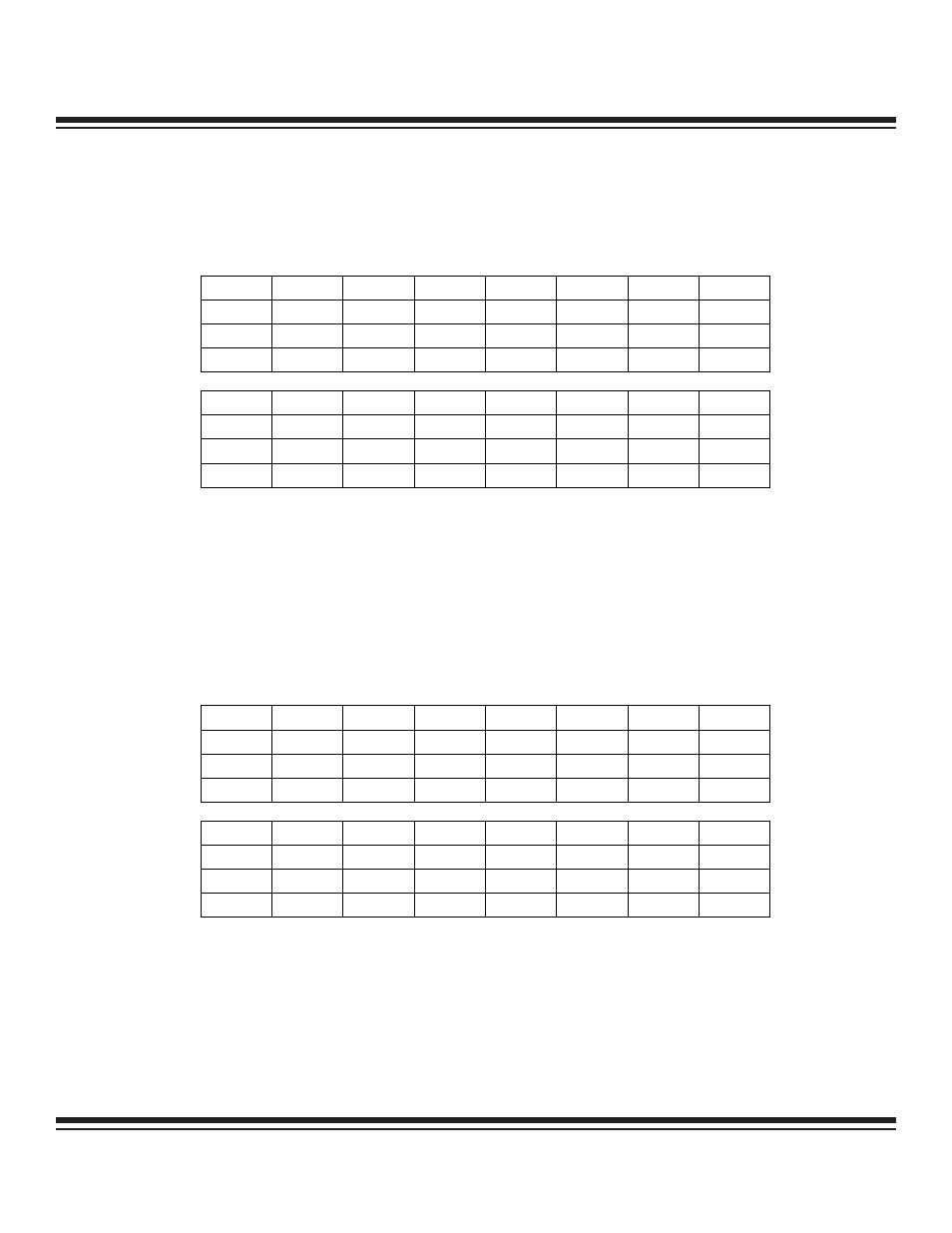

1.4.12 Instruction Pointer Register (IP)

Register Description:

Instruction Pointer Register

Register Name:

IP

Register Address:

Module 0Ch, Index 00h

Bits 15 to 0: Instruction Pointer Register Bits 15 to 0 (IP.15 to IP.0). This register contains the address of the next instruction to be

executed and is automatically incremented by 1 after each program fetch. Writing an address value to this register will cause program

flow to jump to that address. Reading from this register will not affect program flow.

1.4.13 Stack Pointer Register (SP)

Register Description:

Stack Pointer Register

Register Name:

SP

Register Address:

Module 0Dh, Index 01h

Bits 15 to 4: Reserved. Read 0, write ignored.

Bits 3 to 0: Stack Pointer Register Bits 3 to 0 (SP.3 to SP.0). These four bits indicate the current top of the hardware stack, from 0h

to Fh. This pointer is incremented after a value is pushed on the stack and decremented before a value is popped from the stack.

MAXQ7665/MAXQ7666 User’s Guide

1-53

Bit #

15 14 13 12 11 10 9 8

Name

IP.15 IP.14 IP.13 IP.12 IP.11 IP.10 IP.9 IP.8

Reset

1 0 0 0 0 0 0 0

Access rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

IP.7 IP.6 IP.5 IP.4 IP.3 IP.2 IP.1 IP.0

Reset

0 0 0 0 0 0 0 0

Access rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Note: This register is cleared to 8000h on all forms of reset.

Bit #

15 14 13 12 11 10 9 8

Name

—

—

—

—

—

—

—

—

Reset

0 0 0 0 0 0 0 0

Access r

r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name

— — — —

SP.3

SP.2

SP.1

SP.0

Reset

0 0 0 0 1 1 1 1

Access r

r

r

r

rw

rw

rw

rw

r = read, w = write

Note: This register is cleared to 000Fh on all forms of reset.

Maxim Integrated