2 can control/status/mask register descriptions -9, 2 control/status/mask register descriptions – Maxim Integrated MAXQ7666 User Manual

Page 139

MAXQ7665/MAXQ7666 User’s Guide

4-9

4.2.2 Control/Status/Mask Register Descriptions

The CAN control/status/mask registers are located at either the higher order (H) or the lower order (L) byte of the dual port address

location from 00h to 07h. Write access to these registers in dual port memory space is allowed only during a software initialization

(SWINT = 1). A write by the microcontroller to any of these registers when SWINT = 0 will not alter any of the data in these registers.

The CAN control/status/mask registers can be read at any time independent of the state of SWINT. All the CAN control/status/mask reg-

isters are cleared to 00h after system reset.

All the dual port memory locations are accessed by the microcontroller through the CAN 0 data pointer and CAN 0 data buffer regis-

ters located in the peripheral register map.

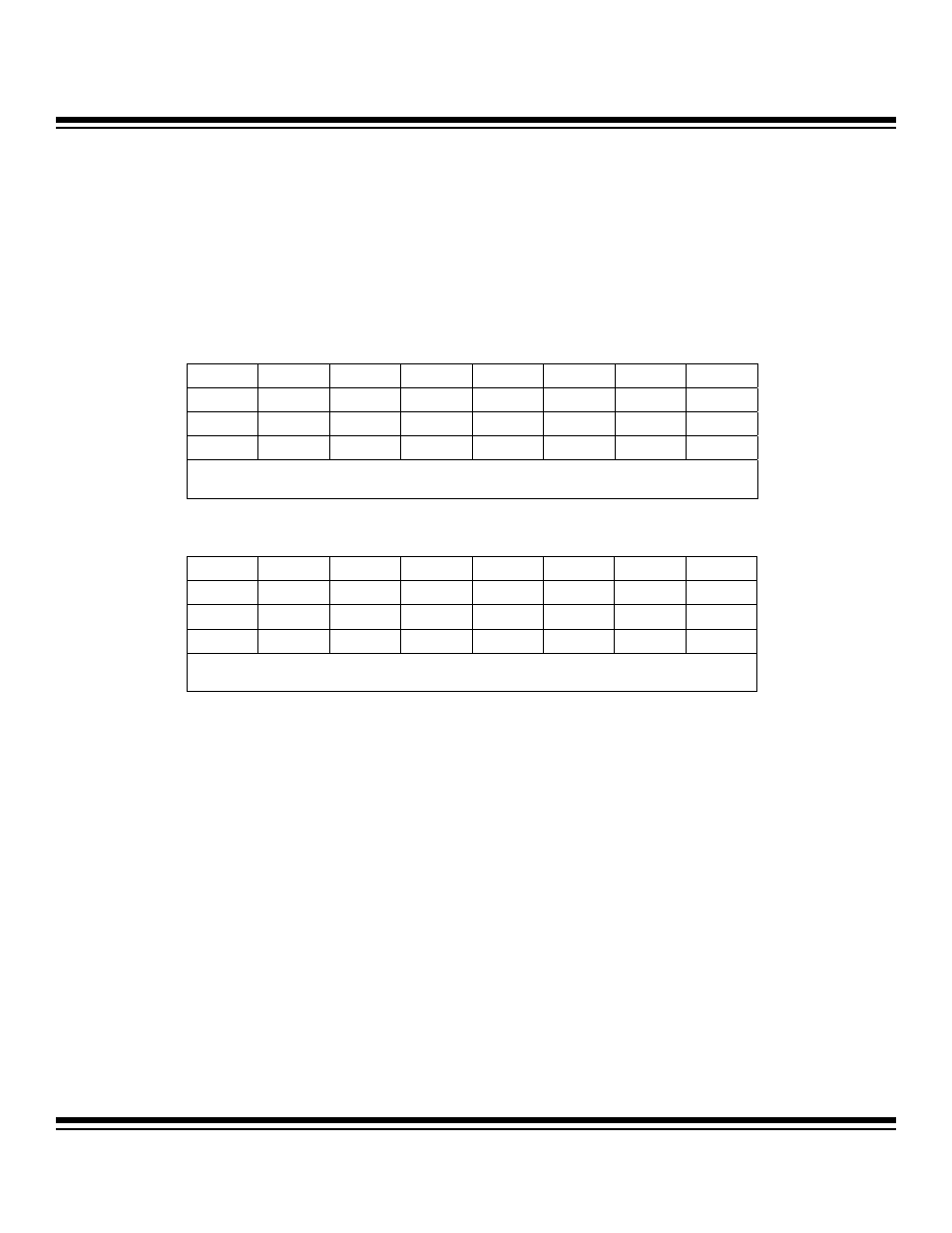

CAN 0 Media ID Mask Register 0 (C0MID0)

CAN 0 Media ID Mask Register 1 (C0MID1)

CAN 0 Media ID Mask Registers 0 and 1 (C0MID0 and C0MID1). These registers function as the mask when performing the media

identification test. These registers can only be modified during a software initialization (SWINT = 1). If MDME = 0, the media identifi-

cation test cannot be performed, and the contents of these registers is ignored. If MDME = 1, the CAN module performs an addition-

al qualifying test on data bytes 0 and 1 of the incoming message, regardless of the state of the EX/

ST bit. Data byte 1 is compared

against CAN media byte arbitration register 1 using C0MID1 as a mask; data byte 0 is compared against CAN media byte arbitration

register 0 using C0MID0 as a mask. Any bit in the C0MID1, C0MID0 masks programmed to 0 will ignore the state of the correspond-

ing data byte bit when performing the test. Any bit in the C0MID1, C0MID0 masks programmed to 1 will force the state of the corre-

sponding data byte bit and CAN media byte arbitration registers 1 and 0 to match before considering the incoming message a match.

Programming either media ID mask register to 00h effectively disables the media ID test for that byte. As such, the C0MID1, C0MID0

masks act as a don’t care following a system reset.

Bit #

7 6 5 4 3 2 1 0

Name

MID07 MID06 MID05 MID04 MID03 MID02 MID01 MID00

Reset

0 0 0 0 0 0 0 0

Access

rw rw rw rw rw rw rw rw

Dual Port

Address

00h(L)

Bit #

7 6 5 4 3 2 1 0

Name

MID17 MID16 MID15 MID14 MID13 MID12 MID11 MID10

Reset

0 0 0 0 0 0 0 0

Access

rw rw rw rw rw rw rw rw

Dual Port

Address

01h(L)

r = read, w = write (allowed only when SWINT = 1 via C0DP/C0DB)

Maxim Integrated