5 analog interrupt enable register (aie) -11, 5 analog interrupt enable register (aie) – Maxim Integrated MAXQ7666 User Manual

Page 208

Bit 2: Watchdog Reset Flag (WTRF). This flag is set to 1 when the watchdog resets the processor. Software can check this bit fol-

lowing a reset to determine if the watchdog was the source of the reset. Setting this bit to 1 in software will not cause a watchdog reset.

This bit is cleared by power-on reset only and is unaffected by other forms of reset. It should always be cleared by software following

a reset so that the source of the next reset can be correctly determined by software. This bit is only set to 1 when a watchdog reset

actually occurs, so if EWT is cleared to 0 when the watchdog timer elapses, this bit will not be set.

Bit 1: Enable Watchdog Timer Reset (EWT). If this bit is set to 1 when the watchdog timer elapses, the watchdog resets the proces-

sor 512 system clock cycles later unless action is taken to disable the reset event. Clearing this bit to 0 prevents a watchdog reset from

occurring but does not stop the watchdog timer or prevent watchdog interrupts from occurring if EWDI = 1. If EWT = 0 and EWDI = 0,

the watchdog timer will be stopped. If the watchdog timer is stopped (EWT = 0 and EWDI = 0), setting the EWT bit resets the watch-

dog interval and reset counter, and enables the watchdog timer. This bit is cleared on power-on reset and is unaffected by other forms

of reset.

Note: The watchdog timer is clocked by the internal 7.6MHz RC oscillator. Therefore, RCE should be set to 1 for the watchdog timer

operation.

Bit 0: Reset Watchdog Timer (RWT). Setting this bit to 1 resets the watchdog timer count. If watchdog interrupt and/or reset modes

are enabled, the software must set this bit to 1 before the watchdog timer elapses to prevent an interrupt or reset from occurring. This

bit always returns 0 when read.

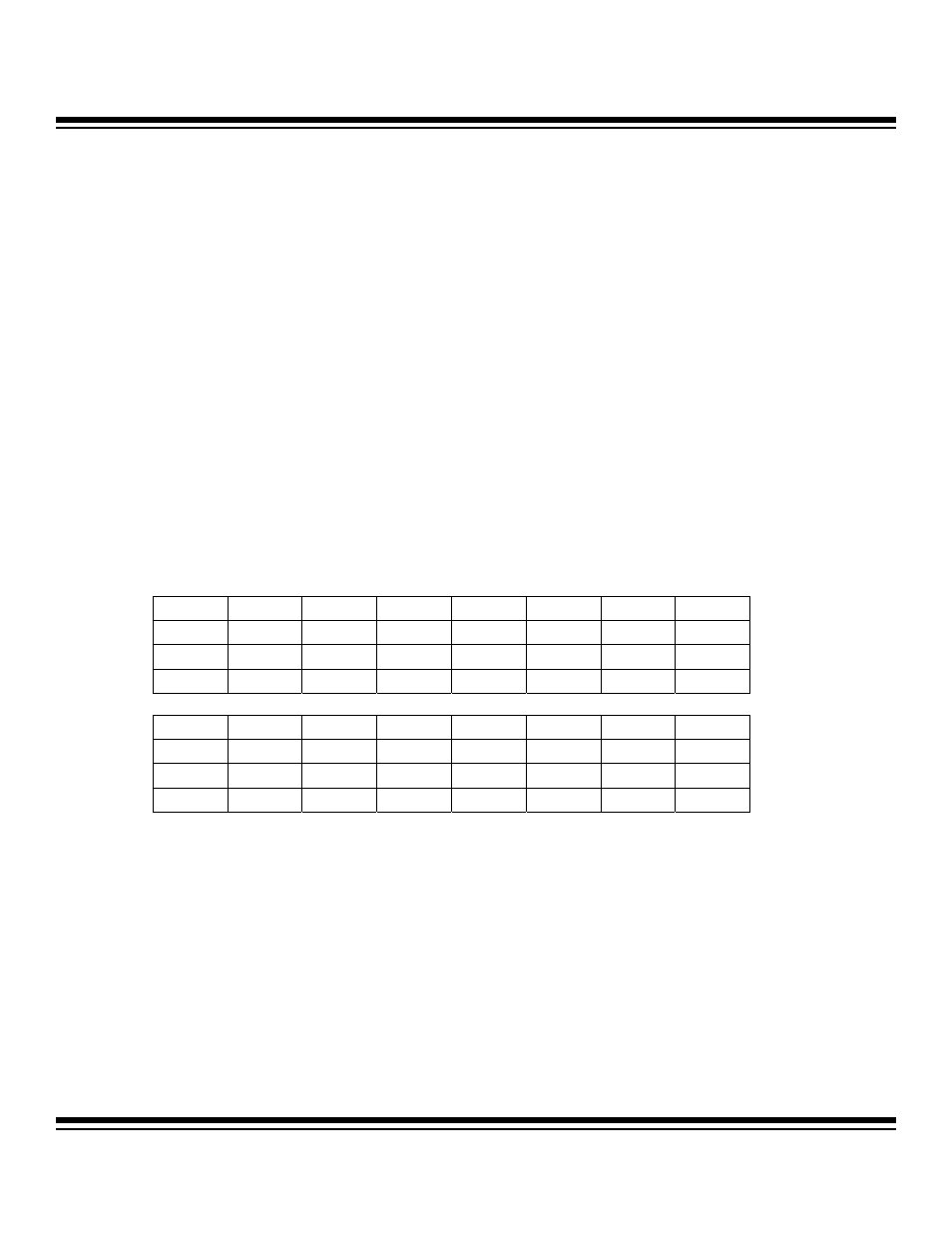

5.2.5 Analog Interrupt Enable Register (AIE)

The AIE register contains the enable bits for various analog interrupts. With respect to the clock generation logic, it contains the enable

bit for high-frequency oscillator failure detection.

Register Description:

Analog Interrupt Enable Register

Register Name:

AIE

Register Address:

Module 05h, Index 0Ah

Bits 15 to 7 and 3: Reserved. Read 0, write ignored.

Bit 6: External High-Frequency Oscillator Failure Interrupt Enable (HFFIE). This bit must be set to logic 1 to generate an interrupt

request when high-frequency oscillator failure is detected and the HFFINT flag in the ASR register is set to logic 1. Clearing this bit to

0 disables the interrupt capability from the HFFINT flag.

Note: To be acknowledged by the microcontroller interrupt logic, this interrupt request must also be enabled by IGE bit in the IC reg-

ister and IM5 mask in the IMR peripheral register.

Bit 5: I/O Voltage Brownout Interrupt Enable (VIOBIE). See

Section 2 for more information on this bit.

Bit 4: Digital Brownout Interrupt Enable (DVBIE). See

Section 2 for more information on this bit.

Bit 2: ADC Overrun Interrupt Enable (AORIE). See

Section 3 for more information on this bit.

Bit 1: ADC Data Ready Interrupt Enable (ADCIE). See

Section 3 for more information on this bit.

Bit 0: This bit is implemented and available to be used as a user-software-controlled bit.

Bit #

15

14

13

12

11

10

9

8

Name — — — — — — — —

Reset 0 0 0 0 0 0 0 0

Access r r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name —

HFFIE

VIOBIE

DVBIE

—

AORIE

ADCIE

—

Reset 0 0 0 0 0 0 0 1

Access r rw

rw

rw

r

rw

rw

rw

r = read, w = write

MAXQ7665/MAXQ7666 User’s Guide

5-11

Maxim Integrated