3 gpio operation -9, 1 port p0 direction control and input/output -9, 2 port p0 external interrupts -9 – Maxim Integrated MAXQ7666 User Manual

Page 271

8.3 GPIO Operation

From a software perspective, the MAXQ7665/MAXQ7666 port P0 appears as a group of peripheral registers with unique addresses and

is addressed as a byte or 8 individual bit locations. The port is designed to provide programming flexibility for the user application.

• All individual I/O bits are independently configured.

• Any combination of input, output, or alternate function in a port is permitted.

• All I/O pins have protection circuitry to VDDIO and ground.

8.3.1 Port P0 Direction Control and Input/Output

The port 0 direction register (PD0) controls the MAXQ7665/MAXQ7666 port P0 pin input/output direction. The port 0 input register (PI0)

is a read-only register that always reflects the logic state on the pins. The port 0 output register (PO0) has a dual function. For pins

defined as output, PO0 stores output data, and for pins defined as input, PO0 controls whether the internal weak pullup is enabled or

disabled. The port P0 pins input/output states in standard mode (no special or alternate function enabled) are according to Table 8-2.

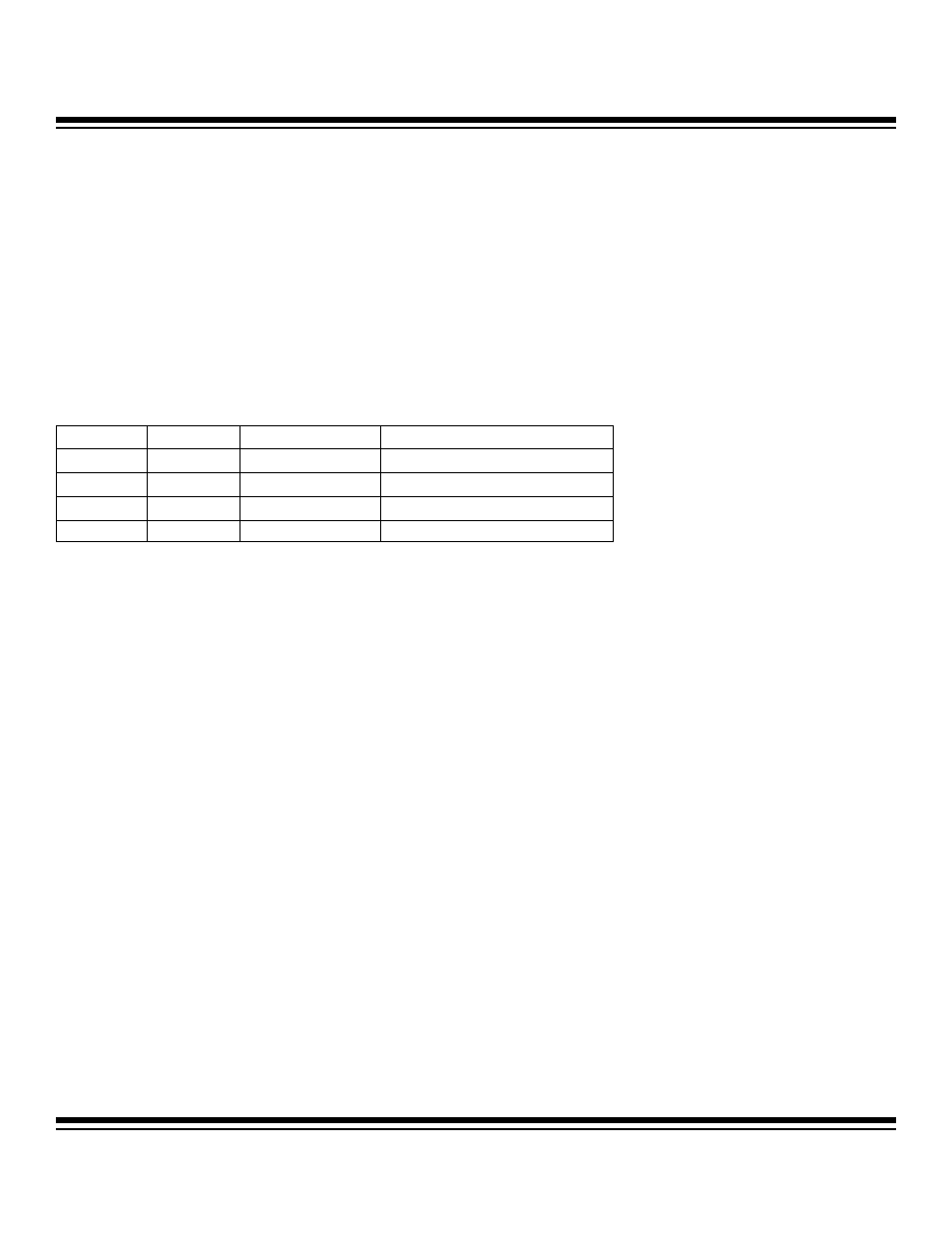

Table 8-2. Port P0 Pin Input/Output States (in Standard Mode)

The port P0 can be used to support applications that require open-drain functionality. This can be achieved by using the PO0 and PD0

register of the port.

• Three-state the port pin needed to be open drain by setting the corresponding PD0 bit to 0.

• Clear the corresponding PO0 bit to 0.

• Use the corresponding PD0 bit to drive the port pin function, instead of the 00 register.

Note that the internal pullup has a relatively high impedance (typically ˜400kΩ), so a particular system may require a stronger (exter-

nal) pullup to meet the system level needs.

8.3.2 Port P0 External Interrupts

Each of the port P0 pins can function as an external interrupt with individual enable, flag, and active edge selection bits.

• External interrupt enable register (EIE0) bits determine if the external interrupt functionality at each pin is enabled or not.

• External interrupt edge select register (EIES0) bits determine if the external interrupt is generated on rising or falling edge of the

interrupt pin input.

• External interrupt flag register (EIF0) bits indicate if a valid rising or falling edge has been detected on the interrupt pin input. An

interrupt is generated only if the external interrupt functionality is enabled for the pin. Also, global interrupt mask bits IM0 (in the

IMR register) and IGE (in the IC register) must be enabled.

Note: The detection of a valid interrupt edge on any of the external interrupt pins can act as a switchback-trigger source, causing the

microcontroller to switch back from power management mode (PMME = 1, clock set to divide-by-256) to the standard divide-by-1 sys-

tem clock frequency.

8.3.3 Port P0 Special and Alternate Functions

All the MAXQ7665/MAXQ7666’s port pins are multiplexed with special functions as listed in Table 8-3. All these special functions are

disabled by default with the exception of the JTAG interface pins, which are enabled by default following any reset. The behavior of

these functions breaks down into two categories:

• Special functions override the PD0 and PO0 settings for the port pin when they are enabled. Once the special function takes con-

trol, normal control of the port pin is lost until the special function is disabled. Examples of special functions include timer 0 and

timer 1 output.

• Alternate functions operate in parallel with PD0 and PO0 settings for the port pin, and generally consist of input-only functions

such as external interrupts. When an alternate function is enabled for a port pin, the port pin’s output state is still controlled in the

usual manner.

MAXQ7665/MAXQ7666 User’s Guide

8-9

PD0.x

PO0.x

PORT PIN MODE

PORT PIN (P0.x) STATE

0 0

Input

Three-state

0

1

Input

Weak pullup HIGH

1 0 Output

Strong

drive

LOW

1

1

Output

Strong drive HIGH

Maxim Integrated