4 dr-scan sequence -8, 5 communication via tap -8, Table 10-3. instruction register commands -8 – Maxim Integrated MAXQ7666 User Manual

Page 294: Communication via tap, Table 10-3. instruction register commands, 4 dr-scan sequence

10.4.4 DR-Scan Sequence

Once the instruction register has been configured to a desired state (mode), transactions are performed via a data buffer register asso-

ciated with that mode. These data transactions are executed serially in a manner analogous to the process used to load the instruc-

tion register. The transactions are grouped in the TAP controller state sequence starting from the select-DR-scan state. In the TAP con-

troller state sequence, the shift-DR state allows internal data to be shifted out through the TDO pin while the external data is shifted in

simultaneously via the TDI pin. Once a complete data pattern is shifted in, input data can be latched into the parallel buffer of the

selected register on the falling edge of TCK in the update-DR state. On the same TCK falling edge, in the update-DR state, the inter-

nal parallel buffer is loaded to the data shift register for output. This shift-DR/update-DR process serves as the basis for passing infor-

mation between the external host and the MAXQ7665/MAXQ7666. These data register transactions occur in the data register portion

of the TAP controller state sequence diagram and have no effect on the instruction register.

10.

4.5

Communication via TAP

The TAP controller is in test-logic-reset state after a power-on-reset. During this initial state, the instruction register contains bypass

instruction and the serial path defined between the TDI and TDO pins for the shift-DR state is the 1-bit bypass register. All TAP signals

(TCK, TMS, TDI, and TDO) default to being weakly pulled high internally on any reset. The TAP controller remains in the test-logic-reset

state as long as TMS is held high. The TCK and TMS signals can be manipulated by the host to transition to other TAP states. The TAP

controller remains in a given state whenever TCK is held low.

For the host to establish a specific data communication link, a private instruction must be loaded into the IR2:IR0 register. Once the

instruction is latched in the instruction parallel buffer at the update-IR state, it is recognized by the TAP controller and the communi-

cation channel is established. In-circuit debug or in-system programming commands and data can be exchanged between the host

and the MAXQ7665/MAXQ7666 by operating in the data register portion of the state sequence (i.e., DR-scan). The TAP retains the pri-

vate instruction that was loaded into IR2:IR0 until a new instruction is shifted in or until the TAP controller returns to the test-logic-reset

state.

MAXQ7665/MAXQ7666 User’s Guide

10-8

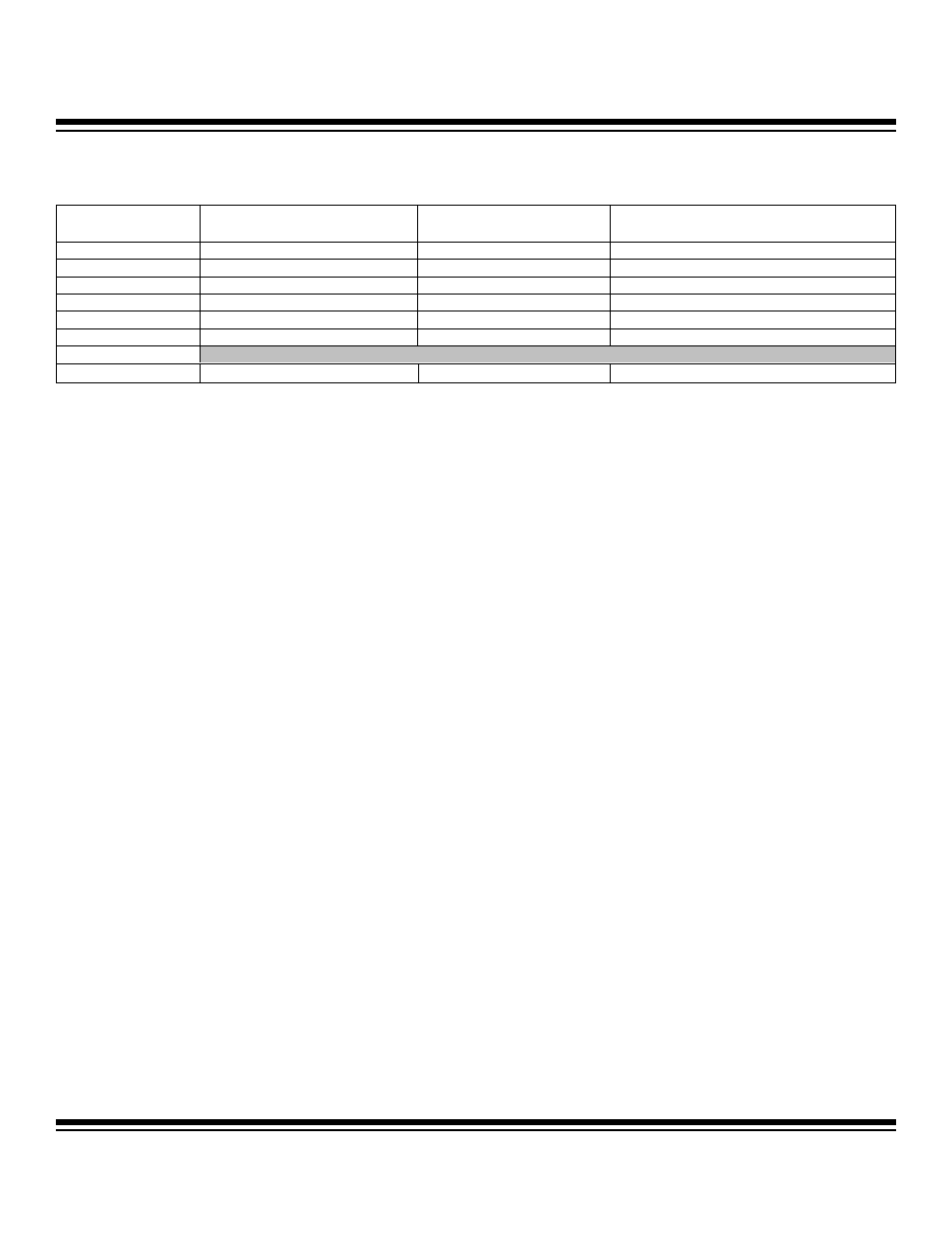

Table 10-3. Instruction Register Commands

IR2:IR0

INSTRUCTION

FUNCTION

SERIAL DATA SHIFT

REGISTER SELECTION

0

0

0

Extest

No operation

Unchanged (retain previous selection)

0

0

1

Sample/Preload

No operation

Unchanged (retain previous selection)

0

1

0

Debug

In-circuit debug mode

10-bit shift register

0

1

1

Bypass

No operation (default)

1-bit shift register

1

0

0

System Programming

Bootstrap function

3-bit shift register

1

0

1

Bypass

No operation (default)

1-bit shift register

1

1

0

Reserved

1

1

1

Bypass

No operation (default)

1-bit shift register

Maxim Integrated