2 measure high-pulse duration repeatedly -23 – Maxim Integrated MAXQ7666 User Manual

Page 258

MAXQ7665/MAXQ7666 User’s Guide

7-23

7.4.2 Measure High-Pulse Duration Repeatedly

To measure the duration of high pulses seen on the T0 input pin repeatedly, the Type 2 timer is configured for a single-shot delayed

run, gating enabled for logic-low, and capture on the falling edge. The CPRL2 bit can be set to generate a reload on each falling edge.

; ------------------ Reset State: T2R0 = T2V0 = T2C0 = 0000h ------------------------

MOVE T2CFG0, #00000100b

;

; T2DIV[2:0]

=000

(/1)

; T2MD

=0

(16-bit)

; CCF[1:0]

=10

(falling edge)

; C/T2

=0

(timer/capture)

MOVE T2CNA0, #10001111b

; ET2

=1

(enable Timer ints)

; T2OE0

=0

(input)

; T2POL0

=0

(gating level = ‘0’)

; TR2L:TR2

=01

(start timer on single shot

;

condition)

; CPRL2

=1

(reload on capture edge)

; SS2

=1

(single shot mode)

; G2EN

=1

(gating enabled)

; ------------------ TCC2 Interrupt : DURATION = T2C0

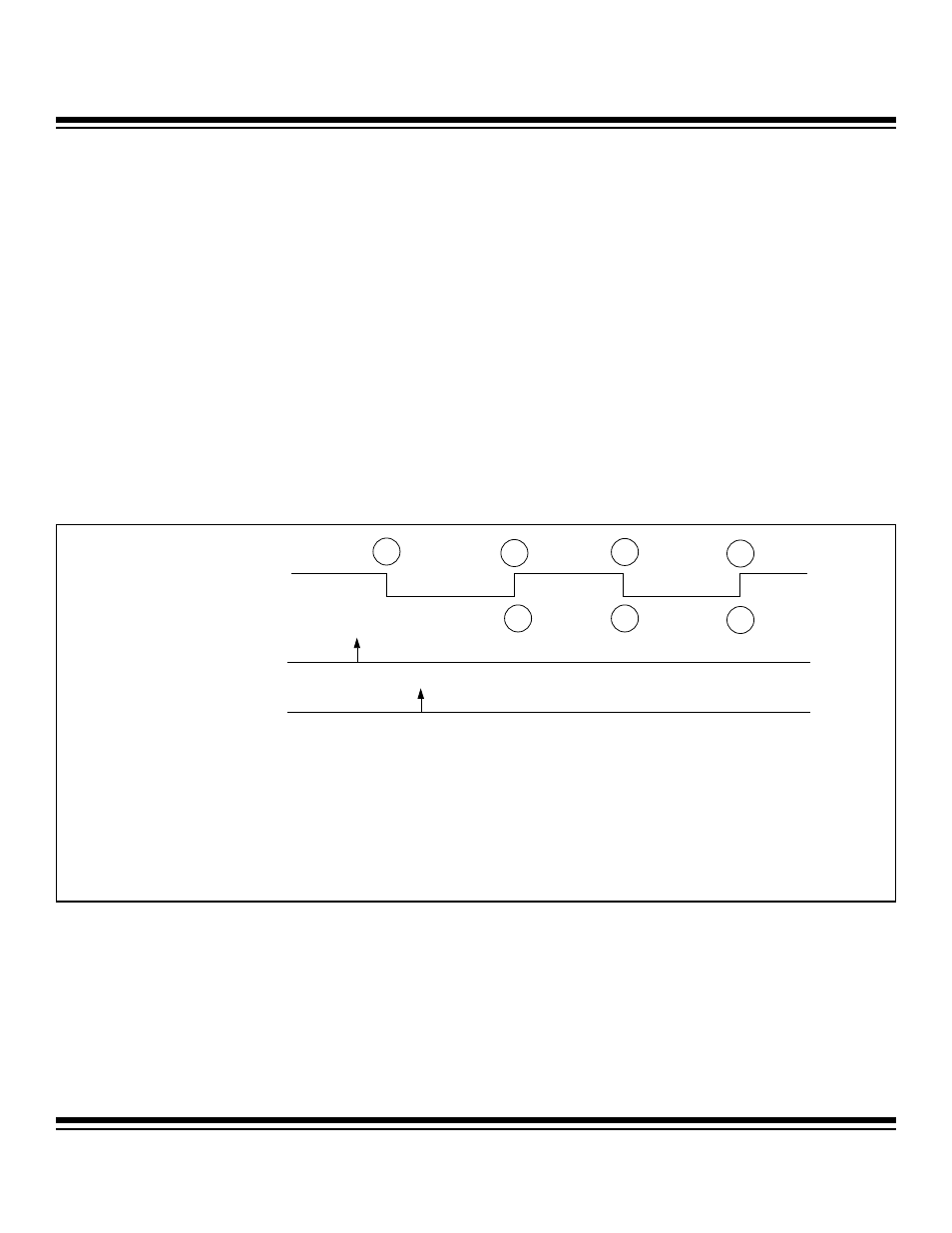

EVENTS:

1A: FALLING EDGE CAUSES CAPTURE/RELOAD; SINGLE-SHOT CAPTURE CYCLE BEGINS; TIMER CLOCK GATED SINCE T0 PIN = 0.

2A: GATING CONDITION REMOVED; TIMER RUNS.

3A: FALLING EDGE CAUSES CAPTURE/RELOAD; SINGLE-SHOT CAPTURE CYCLE ENDS; DURATION = T2C0. TIMER CONTINUES TO OPERATE

SINCE TR2 = 1, BUT TIMER CLOCK GATED SINCE T0 PIN = 0.

4A: GATING CONDITION REMOVED; TIMER RUNS.

1B: GATING CONDITION REMOVED; SINGLE-SHOT CAPTURE CYCLE BEGINS.

2B: FALLING EDGE CAUSES CAPTURE/RELOAD; SINGLE-SHOT CAPTURE CYCLE ENDS; DURATION = T2C0. TIMER CONTINUES TO OPERATE

SINCE TR2 = 1, BUT TIMER CLOCK GATED SINCE T0 PIN = 0.

3B: GATING CONDITION REMOVED; TIMER RUNS.

T0 PIN

CODE EXECUTION:

POINT A

CODE EXECUTION:

POINT B

1A

2A

1B

2B

3B

3A

4A

Figure 7-7. Type 2 Timer Application Example—Measure High Pulse Width

Maxim Integrated