2 in-circuit debug peripheral registers -4, 1 in-circuit debug temporary 0 register (icdt0) -4, 2 in-circuit debug peripheral registers – Maxim Integrated MAXQ7666 User Manual

Page 300: 1 in-circuit debug temporary 0 register (icdt0)

The debug engine is supported by five functional registers:

• ICDB: The ICDB register is an 8-bit data register that supports exchanging command/data between the host system and the in-

circuit debugger. The register functions as an 8-bit parallel buffer for the debug shift register in the TAP. The ICDB register is

mapped to the peripheral register space and is read/write accessible by the CPU and the debug engine.

• ICDC: The ICDC register is an 8-bit control register for the in-circuit debugger. All bits in this register are set/reset by the debug

engine. It is mapped to the peripheral register space and is read only by the CPU.

• ICDF: The ICDF register is an 8-bit register and is used to provide system status to the host system, the debug engine, and the

CPU during debug operation. This register is mapped to the peripheral register space and read/write accessible by the CPU and

the debug engine.

• ICDA: The ICDA register is a 16-bit register that is primarily used to specify an address for ROM assisted operations. The ICDA

is mapped to the peripheral register space and is read only by the CPU. It is read/write accessible by the debug engine. The

ICDA may also be used as a bit mask for register access breakpoints (REGE = 1).

• ICDD: The ICDD register is a 16-bit register that is used to store data for ROM assisted operations. The ICDD is mapped to the

peripheral register space and is read only by the CPU. It is read/write accessible by the debug engine. The ICDD may also be

used as the bit compare match data for register access breakpoints (REGE = 1).

11.2 In-Circuit Debug Peripheral Registers

The MAXQ7665/MAXQ7666 in-circuit debug peripheral registers are described here. All the in-circuit debug peripheral registers are

directly accessible by the microcontroller through the module/index address.

11.2.1 In-Circuit Debug Temporary 0 Register (ICDT0)

The ICDT0 register is read/write accessible by the CPU only in background mode or debug mode. This register is intended for use by

the utility ROM routine as temporary storage to save registers that might otherwise have to be placed in the stack. This register is

cleared after a power-on reset or by a test-logic-reset TAP state.

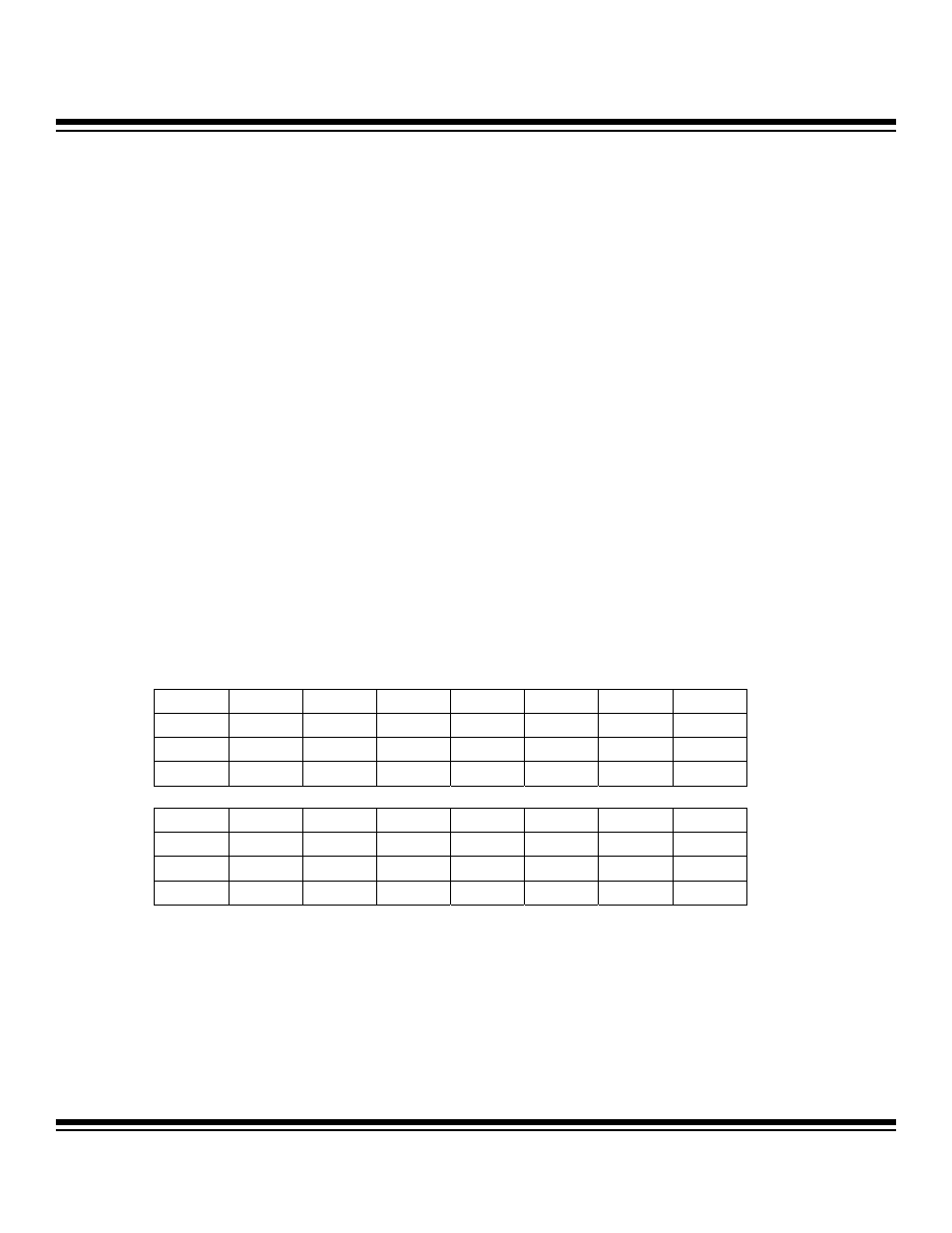

Register Description:

In-Circuit Debug Temporary 0 Register

Register Name:

ICDT0

Register Address:

Module 02h, Index 18h

Bits 15 to 0: In-Circuit Debug Temporary 0 Register Bits 15 to 0 (ICDT0.15 to ICDT0.0)

MAXQ7665/MAXQ7666 User’s Guide

11-4

Bit #

15

14

13

12

11

10

9

8

Name

ICDT0.15 ICDT0.14 ICDT0.13 ICDT0.12 ICDT0.11 ICDT0.10 ICDT0.9 ICDT0.8

Reset

0 0 0 0 0 0 0 0

Access s s s s s s s s

Bit #

7

6

5

4

3

2

1

0

Name

ICDT0.7 ICDT0.6 ICDT0.5 ICDT0.4 ICDT0.3 ICDT0.2 ICDT0.1 ICDT0.0

Reset

0 0 0 0 0 0 0 0

Access s s s s s s s s

s = special (read/write access only in background or debug mode)

Maxim Integrated